- 全部分類

- 集成電路(IC)

- 開發板,套件,編程器

- 分立半導體產品

- 板安裝電源

- 射頻和無線

- 傳感器,變送器

- 存儲卡,模塊

- 音頻產品

- 電路保護

- 晶體,振蕩器,諧振器

- 濾波器

- 隔離器

- 套件

- 創客/DIY,教育

- 光電器件

- 電源 - 外部/內部(板外)

- 繼電器

- 電阻器

- 測試與計量

- 未分類

- 連接器,互連器件

- 電感器,線圈,扼流圈

- 電機,電磁閥,驅動器板/模塊

- 交換機

- 電纜組件

- 嵌入式計算機

- 電容器

- 風扇,熱管理

- 變壓器

- 電池產品

- 產品

- 制造商

- 服務範圍

- 服務行業

- 質量保證承諾

- 資源

LFECP10E-3Q208C datasheet

LFECP10E-3Q208C pdf

LFECP10E-3Q208C distributor

LFECP10E-3Q208C manufacturer

LFECP10E-3Q208C supplier

LFECP10E-3Q208C price

LFECP10E-3Q208C specification

LFECP10E-3Q208C wholesale

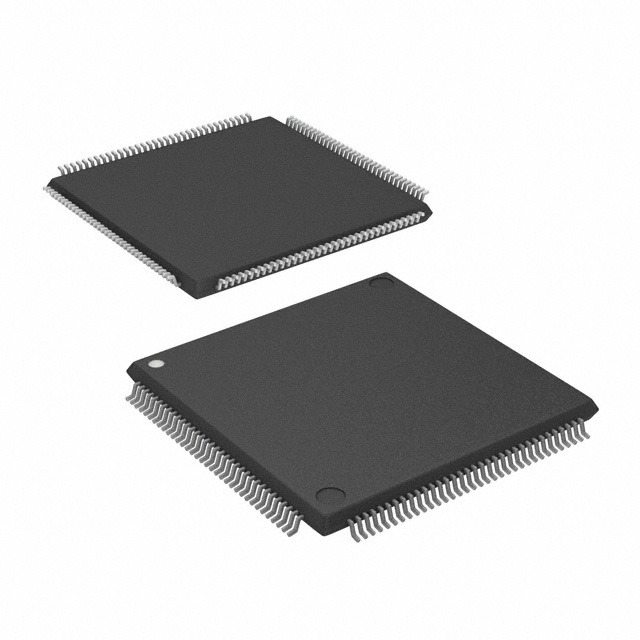

LFECP10E-3Q208C package

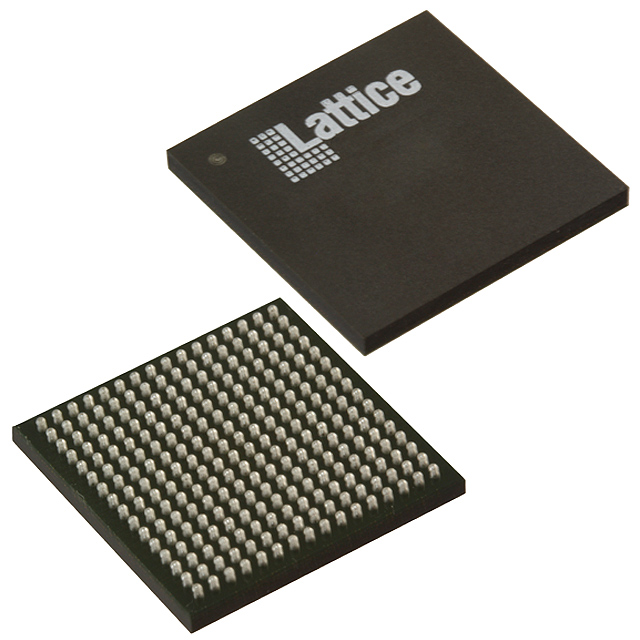

LFECP10E-3Q208C Lattice Semiconductor Corporation

LFECP10E-3Q208C

面議

價格更新:一個月前

Lattice Semiconductor Corporation

Lattice Semiconductor 是低功耗可編程的領導者。 在不斷增長的通信、計算、工業、汽車和消費市場中,他們通過網絡解決客户問題,從邊緣到雲端。 他們的技術、長期合作關係以及對世界級支持的承諾讓他們的客户能夠快速、輕鬆地釋放他們的創新,以創造一個智能、安全和互聯的世界。

查看所有産品從 Lattice Semiconductor Corporation熱門産品

The LatticeECP/EC family of FPGA devices has been optimized to deliver mainstream FPGA features at low cost. For maximum performance and value, the LatticeECP (EConomy Plus) FPGA concept combines an efficient FPGA fabric with high-speed dedicated functions. Lattice’s first family to implement this approach is the LatticeECP-DSP (EConomy Plus DSP) family, providing dedicated high-performance DSP blocks on-chip. The LatticeEC™ (EConomy) family supports all the general purpose features of LatticeECP devices without dedicated function blocks to achieve lower cost solutions.

The LatticeECP/EC FPGA fabric, which was designed from the outset with low cost in mind, contains all the critical FPGA elements: LUT-based logic, distributed and embedded memory, PLLs and support for mainstream I/Os. Dedicated DDR memory interface logic is also included to support this memory that is becoming increasingly prevalent in cost-sensitive applications.

The ispLEVER® design tool from Lattice allows large complex designs to be efficiently implemented using the LatticeECP/EC family of FPGA devices. Synthesis library support for LatticeECP/EC is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP/EC device. The ispLEVER tool extracts the timing from the routing and back-annotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE™ modules for the LatticeECP/EC family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

Feature

■ Extensive Density and Package Options

• 1.5K to 41K LUT4s

• 65 to 576 I/Os

• Density migration supported

■ sysDSP™ Block (LatticeECP™ Versions)

• High performance multiply and accumulate

• 4 to 10 blocks

− 4 to 10 36x36 multipliers or

– 16 to 40 18x18 multipliers or

− 32 to 80 9x9 multipliers

■ Embedded and Distributed Memory

• 18 Kbits to 645 Kbits sysMEM™ Embedded Block RAM (EBR)

• Up to 163 Kbits distributed RAM

• Flexible memory resources:

− Distributed and block memory

■ Flexible I/O Buffer

• Programmable sysIO™ buffer supports wide range of interfaces:

− LVCMOS 3.3/2.5/1.8/1.5/1.2

− LVTTL − SSTL 3/2 Class I, II, SSTL18 Class I

− HSTL 18 Class I, II, III, HSTL15 Class I, III

− PCI

− LVDS, Bus-LVDS, LVPECL, RSDS

■ Dedicated DDR Memory Support

• Implements interface up to DDR400 (200MHz)

■ sysCLOCK™ PLLs

• Up to 4 analog PLLs per device

• Clock multiply, divide and phase shifting

■ System Level Support

• IEEE Standard 1149.1 Boundary Scan, plus ispTRACY™ internal logic analyzer capability

• SPI boot flash interface

• 1.2V power supply

■ Low Cost FPGA

• Features optimized for mainstream applications

• Low cost TQFP and PQFP packaging

- 1. 起步價為$40,南非、巴西、印度、巴基斯坦、以色列等國家的價格會有所變動,詳情請咨詢相關客服人員。

- 2. 包裹重量≤0.5kg的基本運費根據時區和國家而定。

- 1. 我們的產品目前使用DHL,順豐和UPS運輸。如果數量少,則選擇聯邦快遞。

- 1. 一旦發貨,預期交貨時間跟選擇的運輸方式有所變動。

SZC 的物流和庫存管理計劃為您帶來無與倫比的成功。

我們位於福田、龍崗、南山的戰略樞紐為特定客戶的需求提供各種定制方案。

我們還與主要物流承運商建立了長期合作關係,並提供靈活的解決方案,以滿足您的個性化需求。

1. 您從我們這裡購買的每個電子組件都帶有365天保修期。我們對我們產品的質量負責。

2. 如果您收到的任何物品不處於完美狀態,我們承諾負責任地安排退款或更換。請注意,物品必須處於原始狀態,這些選項才可用。

常見問題解答:

Q: 芯能王電子有限公司如何確保LFECP10E-3Q208C是由真正製造或分銷的?

A: 我們的專業商務發展部門對原始製造商和的代理進行嚴格的測試和資格驗證。所有供應商必須通過我們的資格審查後,才允許在我們的平台上列出他們的LFECP10E-3Q208C設備。我們將LFECP10E-3Q208C產品的採購渠道和質量置於一切之上,確保徹底的供應商審計,以便您可以充滿信心地進行購買。

Q: 我在哪裡可以找到關於LFECP10E-3Q208C晶片的詳細信息,包括原始製造商詳情、FPGA(現場可編程門陣列)應用和圖片?

A: 使用芯能王電子有限公司的智能搜索引擎,按FPGA(現場可編程門陣列)類別過濾,或者瀏覽的品牌頁面以獲取全面信息。

Q: 的LFECP10E-3Q208C在平台上顯示的價格和庫存水平準確嗎?

A: 由於的庫存出現重大波動,實時更新具有挑戰性。然而,我們確保在24小時內進行定期更新。我們建議在進行付款之前,與芯能王電子有限公司的銷售代表或通過我們的在線客服確認您的LFECP10E-3Q208C訂單。

Q: 芯能王電子有限公司接受哪些支付方式?

A: 我們接受多種支付方式,包括TT銀行、PayPal、信用卡、西聯匯款和託管。

Q: 如何安排發貨,並且我如何跟踪我的包裹?

A: 客戶可以從行業領先的貨運公司中選擇,如DHL、FedEx、UPS、TNT和掛號郵件。一旦您的訂單準備好發貨,我們的銷售團隊將通知您發貨詳情並提供跟踪號碼。請注意,跟踪信息可能需要多達24小時才能顯示。通常,快遞交付需要3-5天,而掛號郵件需要25-60天。

Q: LFECP10E-3Q208C的退貨或更換過程是怎樣的?

A: 我們對您訂單中隨機選取的批次進行發貨前檢查(PSI),以確保發貨前的質量。如果LFECP10E-3Q208C未能達到您的期望,在以下條件下,我們將接受退貨或更換:

- 我們承認諸如數量不正確、交付錯誤物品或明顯的外部缺陷等問題。

- 我們在交貨日期後的90天內被告知缺陷。

- LFECP10E-3Q208C保持未使用狀態並且在其原始包裝中。 要啟動退貨前,請:

- 在90天期限內通知我們。

- 獲取退貨授權請求。

- 更多詳情,請參閱我們的退貨及更換政策。

Q: 我如何獲得支持或請求LFECP10E-3Q208C的數據表和引腳圖?

A: 對於任何售後服務,包括LFECP10E-3Q208C的數據表和引腳圖,隨時通過[email protected]與我們聯繫

Q: 我如何聯繫芯能王電子有限公司?請提供具體的聯繫方式。

A: 通過點擊我們網站右下角的客戶服務按鈕,直接提交RFQ,或使用我們頁面頂部的“聯繫我們”鏈接通過電子郵件或電話與我們聯繫。我們保證在24小時內回覆您的查詢。

相關產品

| 製造商零件編號 | 價格(¥) | 現有數量 | |

|---|---|---|---|

LFEC3E-5Q208CIC FPGA 145 I/O 208QFP | 面議 |

2383

市場 | |

LFEC10E-3FN484IIC FPGA 288 I/O 484FBGA | 85.00 |

2250

市場 | |

LFEC3E-4TN144CIC FPGA 97 I/O 144TQFP | 10.00 |

2278

市場 | |

LFEC3E-3TN144CIC FPGA 97 I/O 144TQFP | 25.00 |

4920

市場 |

產品屬性

| 類型 | 描述 | 全選 |

|---|---|---|

| 電壓 - 供電 | 1.14V ~ 1.26V | |

| 安裝類型 | 表面貼裝型 | |

| 系列 | ECP | |

| 工作温度 | 0°C ~ 85°C(TJ) | |

| 包裝 | 託盤 | |

| 封裝/外殼 | 208-BFQFP | |

| 產品狀態 | 停產 | |

| 供應商器件封裝 | 208-PQFP(28x28) | |

| 可編程 | 未驗證 | |

| 邏輯元件/單元數 | 10200 | |

| 總 RAM 位數 | 282624 | |

| I/O 數 | 147 |

部落格

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。

美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。 薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。 三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。

美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。 薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。 三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

面議

價格更新:一個月前

Lattice Semiconductor Corporation

Lattice Semiconductor 是低功耗可編程的領導者。 在不斷增長的通信、計算、工業、汽車和消費市場中,他們通過網絡解決客户問題,從邊緣到雲端。 他們的技術、長期合作關係以及對世界級支持的承諾讓他們的客户能夠快速、輕鬆地釋放他們的創新,以創造一個智能、安全和互聯的世界。

查看所有産品從 Lattice Semiconductor Corporation熱門産品

部落格

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。

美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。 薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。 三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王電子有限公司祝您感恩節快樂感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型訓練方面的強大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪個更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。

美國十大微控制器製造商本文章主要介绍美国前十微控制器制造商。 薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜與陶瓷:選擇適合您的電容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美國十大射頻混頻器製造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

熱烈祝賀芯能王電子榮獲「國際潛力之星分銷商」獎項!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:終極電感式傳感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美國十大陶瓷過濾器製造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。 三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

三星存儲晶片困境:市場動蕩與減產在全球需求波动中,了解市场变化对三星存储芯片生产的影响。

- 無源衰減器與有源衰減器: 區別是什麼?在电子领域,特别是当深入信号处理的深处时,无源和有源衰减器这两个英雄开始发挥重要作用。本文将介绍这两种衰减器的作用和主要区别。

- PIC16F18877微控制器介紹在本文中,我们将深入探讨PIC16F18877 微控制器的核心,探索其主要功能,了解其应用。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。

晶片短缺對手機行業的影響智能手机行业正处于十字路口,在不断变化的市场动态中保持领先地位可以决定制造商的成功或失败。 探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。

探索 IRFZ44N MOSFET:技術愛好者指南今天将揭开 IRFZ44N 背后的秘密,探索其功能,并发现它真正的闪光点。 BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

BC547與 BC548電晶體:有什麼區別?如果您正在深入探索令人着迷的电子世界,您可能听说过BC547和BC548 晶体管这两个型号,今天,我们踏上揭开 BC547 和 BC548 晶体管神秘面纱的旅程,探索它们的差异。

熱門製造商

View all manufactures 更多熱門產品

更多電子零件 更多

ICE40LP384-SG32

IC FPGA 21 I/O 32QFN

LCMXO2-256HC-5SG32C

IC FPGA 21 I/O 32QFNS

ICE40HX1K-VQ100

IC FPGA 72 I/O 100TQFP

ICE40LP1K-CB121

IC FPGA 92 I/O 121CSBGA

ICE40HX4K-BG121

IC FPGA 93 I/O 121CABGA

LCMXO2-1200HC-6TG100C

IC FPGA 79 I/O 100TQFP

LIF-MD6000-6JMG80I

IC FPGA 37 I/O 80CTFBGA

LIA-MD6000-6JMG80E

IC FPGA 37 I/O 80CTFBGA

LCMXO3LF-6900E-6MG256C

IC FPGA 206 I/O 256CSFBGA

LCMXO2-7000HE-4TG144C

IC FPGA 114 I/O 144TQFP