¥650.00

價格更新:一個月前

AMD

AMD是全可編程FPGA、SoC、MPSoC和3D IC的領先提供商。AMD獨特地實現了軟件定義和硬件優化的應用-推動了雲計算,5G無線,嵌入式視覺和工業物聯網領域的行業進步。

查看所有産品從 AMD熱門産品

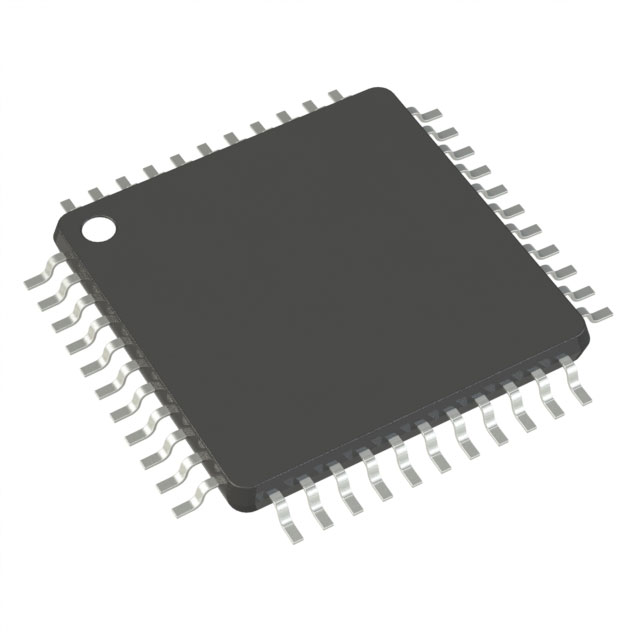

The CoolRunner-II 512-macrocell device is designed for both high performance and low power applications. This lends power savings to high-end communication equipment and high speed to battery operated devices. Due to the low power stand-by and dynamic operation, overall system reliability is improved This device consists of thirty two Function Blocks inter-connected by a low power Advanced Interconnect Matrix (AIM). The AIM feeds 40 true and complement inputs to each Function Block. The Function Blocks consist of a 40 by 56 P-term PLA and 16 macrocells which contain numerous configuration bits that allow for combinational or registered modes of operation. Additionally, these registers can be globally reset or preset and configured as a D or T flip-flop or as a D latch. There are also multiple clock signals, both global and local product term types, configured on a per macrocell basis. Output pin configurations include slew rate limit, bus hold, pull-up, open drain and programmable grounds.

A Schmitt-trigger input is available on a per input pin basis. In addition to storing macrocell output states, the macrocell registers may be configured as "direct input" registers to store signals directly from input pins. Clocking is available on a global or Function Block basis. Three global clocks are available for all Function Blocks as a synchronous clock source. Macrocell registers can be individually configured to power up to the zero or one state. A global set/reset control line is also available to asynchronously set or reset selected registers during operation. Additional local clock, synchronous clock-enable, asynchronous set/reset and output enable signals can be formed using product terms on a per-macrocell or per-Function Block basis. A DualEDGE flip-flop feature is also available on a per macrocell basis. This feature allows high performance synchronous operation based on lower frequency clocking to help reduce the total power consumption of the device. Circuitry has also been included to divide one externally supplied global clock (GCK2) by eight different selections. This yields divide by even and odd clock frequencies.

Feature

產品屬性

| 類型 | 描述 | 全選 |

|---|---|---|

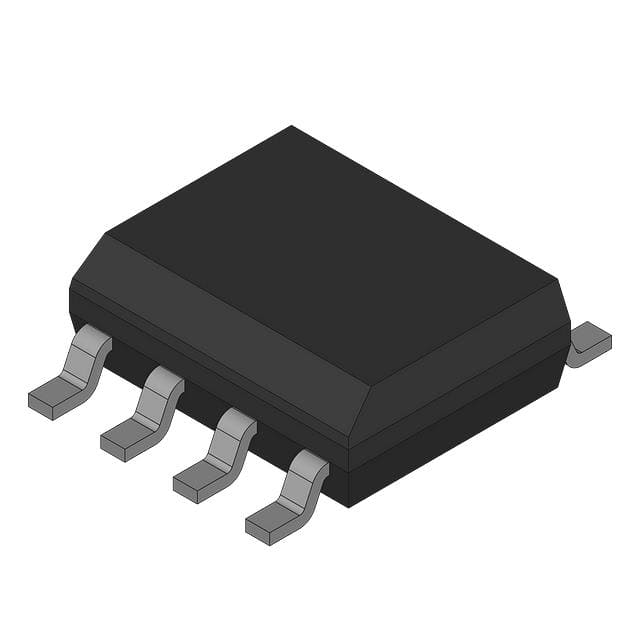

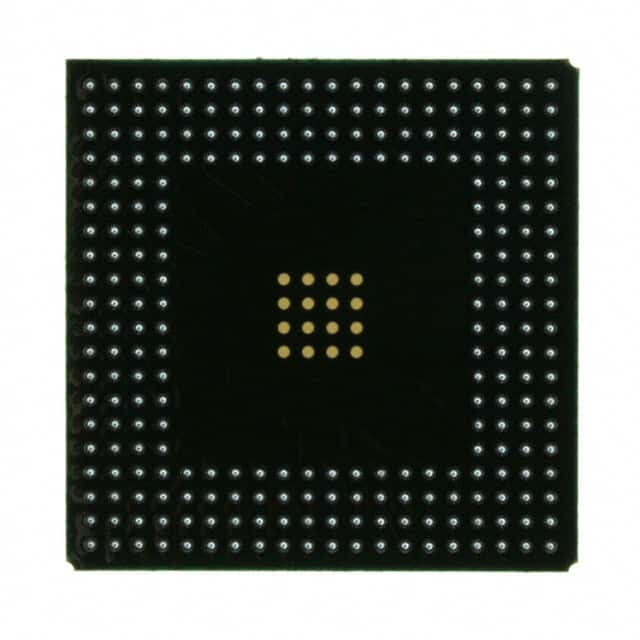

| 封裝/外殼 | 324-BBGA | |

| 可編程 | 未驗證 | |

| 供應商器件封裝 | 324-FBGA(23x23) | |

| 可編程類型 | 系統內可編程 | |

| 延遲時間 tpd(1) 最大值 | 9.2 ns | |

| 供電電壓 - 內部 | 1.7V ~ 1.9V | |

| 邏輯元件/塊數 | 32 | |

| 宏單元數 | 512 | |

| 柵極數 | 12000 | |

| I/O 數 | 270 | |

| 系列 | CoolRunner II | |

| 工作温度 | -40°C ~ 85°C(TA) | |

| 包裝 | 託盤 | |

| 安裝類型 | 表面貼裝型 | |

| 產品狀態 | 在售 |

部落格

¥650.00

價格更新:一個月前

AMD

AMD是全可編程FPGA、SoC、MPSoC和3D IC的領先提供商。AMD獨特地實現了軟件定義和硬件優化的應用-推動了雲計算,5G無線,嵌入式視覺和工業物聯網領域的行業進步。

查看所有産品從 AMD熱門産品

部落格

熱門製造商

View all manufactures 更多熱門產品

更多電子零件 更多

XC2C512-10FGG324I

IC CPLD 512MC 9.2NS 324FBGA

XC2C128-7VQG100C

IC CPLD 128MC 7NS 100VQFP

XCR3256XL-10TQ144I

IC CPLD 256MC 9.1NS 144TQFP

XC2C384-10TQG144C

IC CPLD 384MC 9.2NS 144TQFP

XCR3064XL-10VQG44I

IC CPLD 64MC 9.1NS 44VQFP

XCR3032XL-10VQG44I

IC CPLD 32MC 9.1NS 44VQFP

XCR3064XL-6VQG100C

IC CPLD 64MC 5.5NS 100VQFP

XC2C128-7CPG132I

IC CPLD 128MC 7NS 132CSPBGA

XC95288XL-10TQ144I

IC CPLD 288MC 10NS 144TQFP

XC95288XL-10BG256I

IC CPLD 288MC 10NS 256BGA