¥1.50

價格更新:一個月前

Intersil

自 2018 年 1 月 1 日起,瑞薩電子和 Intersil 將作為一個統一的企業運營,從而顯着擴展半導體的內在能力。 這一組合將廣受好評的瑞薩 MCU 和 SoC 技術與 Intersil 在高性能電源管理和精密模擬器件方面市場領先的專業知識結合在一起。 反過來,這又帶來了汽車、工業和廣泛領域的有機增長,使新企業能夠更快地響應客户的系統需求。 瑞薩電子與 Intersil 的聯合始於 2017 年 2 月 24 日完成收購,統一的「One Global Renesas」於次年 7 月在所有市場投入運營——匯集了兩個組織的優勢,滿足客户需求 快速變化的市場環境。 這個真正的全球組織提供了巨大的協同效應。 加入瑞薩電子,鞏固其在全球半導體市場的領先地位。

查看所有産品從 Intersil熱門産品

CD4047BE consists of a gatable astable multivibrator with logic techniques incorporated to permit positive or negative edge-triggered monostable multivibrator action with retriggering and external counting options.

Inputs include +TRIGGER, -TRIGGER, ASTABLE, ASTABLE\, RETRIGGER, and EXTERNAL RESET.Buffered outputs are Q\, Q and OSCILLATOR.In all modes of operation, and external capacitor must be connected between C-Timing and RC-Common terminal, and an external resistor must be connected between the R-Timing and RC-Common terminals.

Astable operation is enabled by a high level on the STABLE input or a low level on the ASTABLE\ input, or both.The period of the square wave at the Q and Q\ Outputs in this mode off operation is a function of the external components employed."True" input pulses on the ASTABLE input or "Complement" pulses on the ASTABLE\ input allow the circuit to be used as a gatable multivibrator.The OSCILLATOR output period will be half of the Q terminal output in the astable mode.However, a 50% duty cycle is not guaranteed at this output.

The CD4047BE triggers in the monostable mode when a positive-going edge occurs on the +TRIGGER-input while the -TRIGGER is held low.INput pulses may be of any duration relative to the output pulse.

If retrigger capability is desired, the RETRIGGER input is pulsed.The retriggerable mode of operation is limited to positive-going edge.The CD4047BE will retrigger as long as the RETRIGGER-input is high, with or without transitions (See Fig. 34).

An external countdown option can be implemented by coupling "Q" to an external "N" counter and resetting the counter with the trigger pulse.The counter output pulse is fed back to the ASTABLE\ input and has a duration equal to N times the period of the multivibrator.

A high level on the EXTERNAL RESET input assures no output pulse during an "ON" power condition.This input can also be activated to terminate the output pulse at any tine.For monostable operation, whenever VDD is applied, and internal power-on reset circuit will clock the Q output low within one output period (tM).

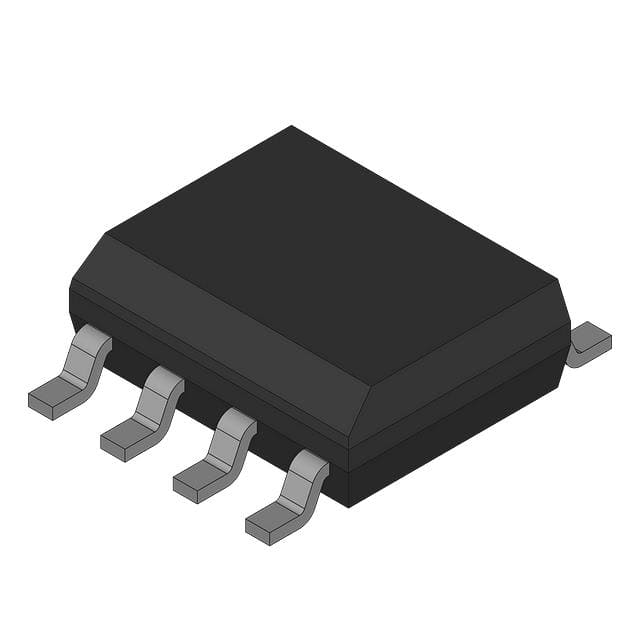

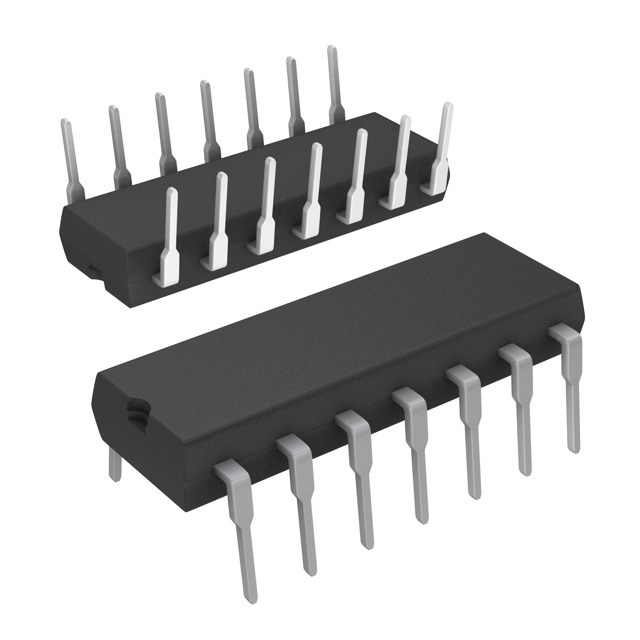

The CD4047B-Series types are supplied in 14-lead hermetic dual-in-line ceramic packages (F3A suffix),14-lead dual-in-line plastic packages (E suffix), 14-lead small outline packages (M, MT, M96, and NSR suffixes),and 14-lead thin shrink small-outline packages (PW and PWR suffixes).

Feature

- Lower power consumption: special CMOS oscillator configuration

- Monostable (one-shot) or astable (free-running) operation

- True and complemented buffered outputs

- Only one external R anc C required

- Buffered inputs

- 100% tested for quiescent current at 20 V

- Standardized, symmetrical output characteristics

- 5-V, 10-V, and 15-V parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

- Monostable Multivibrator Features:

- Positive-or negative-edge trigger

- Output pulse width independent of trigger pulse duration

- Retriggerable option for pulse width expansion

- Internal power-on reset circuit

- Long pulse widths possible using small RC components by means of external counter provision

- Fast recovery time essentially independent of pulse width

- Pulse-width accuracy maintained at duty cycles approaching 100%

- Astable Multivibrator Features:

- Free-running or gatable operating modes

- 50% duty cycle

- Oscillator output available

- Good astable frequency stability: Frequency deviation: = ±2% + 0.03%/°C @ 100 kHz = ±0.5% +0.015%/°C @ 10 kHz (circuits "trimmed" to frequency VDD = 10 V ± 10%)

- Applications: Digital equipment where low-power dissipation and/or high noise immunity are primary design requirements:

- Envelope detection

- Frequency multiplication

- Frequency division

- Frequency discriminators

- Timing circuits

- Time-delay applications

產品屬性

| 類型 | 描述 | 全選 |

|---|---|---|

| 電壓 - 供電 | 3 V ~ 18 V | |

| 電流 - 輸出高、低 | 6.8mA,6.8mA | |

| 施密特觸發器輸入 | 無 | |

| 獨立電路 | 1 | |

| 邏輯類型 | 非穩態,單穩態 | |

| 產品狀態 | 在售 | |

| 包裝 | 管件 | |

| 供應商器件封裝 | 14-PDIP | |

| 系列 | 4000B | |

| 封裝/外殼 | 14-DIP(0.300",7.62mm) | |

| 安裝類型 | 通孔 | |

| 工作温度 | -55°C ~ 125°C | |

| 傳播延遲 | 80 ns |

部落格

¥1.50

價格更新:一個月前

Intersil

自 2018 年 1 月 1 日起,瑞薩電子和 Intersil 將作為一個統一的企業運營,從而顯着擴展半導體的內在能力。 這一組合將廣受好評的瑞薩 MCU 和 SoC 技術與 Intersil 在高性能電源管理和精密模擬器件方面市場領先的專業知識結合在一起。 反過來,這又帶來了汽車、工業和廣泛領域的有機增長,使新企業能夠更快地響應客户的系統需求。 瑞薩電子與 Intersil 的聯合始於 2017 年 2 月 24 日完成收購,統一的「One Global Renesas」於次年 7 月在所有市場投入運營——匯集了兩個組織的優勢,滿足客户需求 快速變化的市場環境。 這個真正的全球組織提供了巨大的協同效應。 加入瑞薩電子,鞏固其在全球半導體市場的領先地位。

查看所有産品從 Intersil熱門産品

部落格

熱門製造商

View all manufactures 更多熱門產品

更多電子零件 更多

CD4047BE

IC MULTIVIBRATOR 80NS 14DIP

JM38510/17504BEA

CD4098B-MIL CMOS DUAL MONOSTABLE

CD4098BE

IC MULTIVIBRATOR 100NS 16DIP

CD74HCT221E

IC MULTIVIBRATOR 18NS 16DIP

TIP42C

TRANS PNP 100V 6A TO220

CD74HC4316M

IC SW SPST-NOX4 170OHM 16SOIC

CA3227M

SMALL SIGNAL BIPOLAR TRANSISTOR

CA3227E

NPN TRANSISTOR ARRAY

CA3083M

GEN PURP NPN TRANSISTOR ARRAYS

ISL6605CB-TS2495

HALF BRIDGE BASED MOSFET DRIVER,