¥45.00

價格更新:一個月前

Lattice Semiconductor Corporation

Lattice Semiconductor 是低功耗可編程的領導者。 在不斷增長的通信、計算、工業、汽車和消費市場中,他們通過網絡解決客户問題,從邊緣到雲端。 他們的技術、長期合作關係以及對世界級支持的承諾讓他們的客户能夠快速、輕鬆地釋放他們的創新,以創造一個智能、安全和互聯的世界。

查看所有産品從 Lattice Semiconductor Corporation熱門産品

Feature

■ High Logic Density for System Integration

• 6K to 95K LUTs

• 90 to 583 I/Os

■ Embedded SERDES (LatticeECP2M Only)

• Data Rates 250 Mbps to 3.125 Gbps

• Up to 16 channels per device PCI Express, Ethernet (1GbE, SGMII), OBSAI, CPRI and Serial RapidIO.

■ sysDSP™ Block

• 3 to 42 blocks for high performance multiply and accumulate

• Each block supports – One 36x36, four 18X18 or eight 9X9 multipliers

■ Flexible Memory Resources

• 55Kbits to 5308Kbits sysMEM™ Embedded Block RAM (EBR)

– 18Kbit block

– Single, pseudo dual and true dual port

– Byte Enable Mode support

• 12K to 202Kbits distributed RAM

– Single port and pseudo dual port

■ sysCLOCK Analog PLLs and DLLs

• Two GPLLs and up to six SPLLs per device

– Clock multiply, divide, phase & delay adjust

– Dynamic PLL adjustment

• Two general purpose DLLs per device

■ Pre-Engineered Source Synchronous I/O

• DDR registers in I/O cells

• Dedicated gearing logic

• Source synchronous standards support

– SPI4.2, SFI4 (DDR Mode), XGMII

– High Speed ADC/DAC devices

• Dedicated DDR and DDR2 memory support

– DDR1: 400 (200MHz) / DDR2: 533 (266MHz)

• Dedicated DQS support

■ Programmable sysI/O™ Buffer Supports Wide Range Of Interfaces

• LVTTL and LVCMOS 33/25/18/15/12

• SSTL 3/2/18 I, II

• HSTL15 I and HSTL18 I, II

• PCI and Differential HSTL, SSTL

• LVDS, RSDS, Bus-LVDS, MLVDS, LVPECL

■ Flexible Device Configuration

• 1149.1 Boundary Scan compliant

• Dedicated bank for configuration I/Os

• SPI boot flash interface

• Dual boot images supported

• TransFR™ I/O for simple field updates

• Soft Error Detect macro embedded

■ Optional Bitstream Encryption (LatticeECP2/M “S” Versions Only)

■ System Level Support

• ispTRACY™ internal logic analyzer capability

• On-chip oscillator for initialization & general use

• 1.2V power supply

產品屬性

| 類型 | 描述 | 全選 |

|---|---|---|

| 電壓 - 供電 | 1.14V ~ 1.26V | |

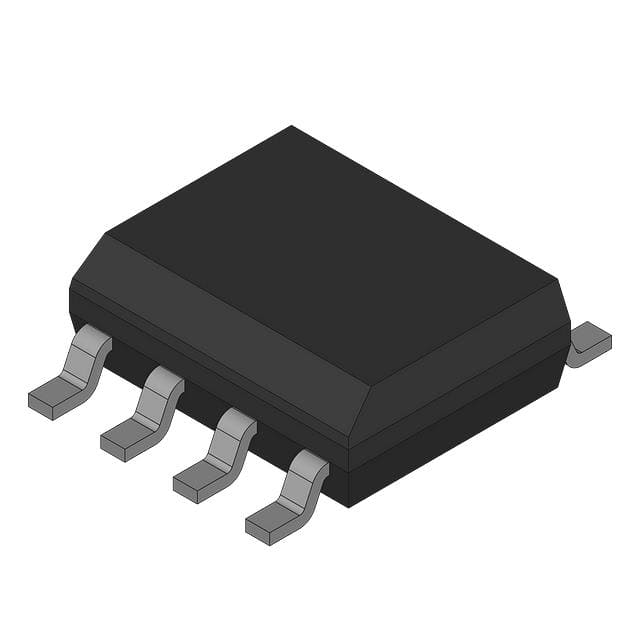

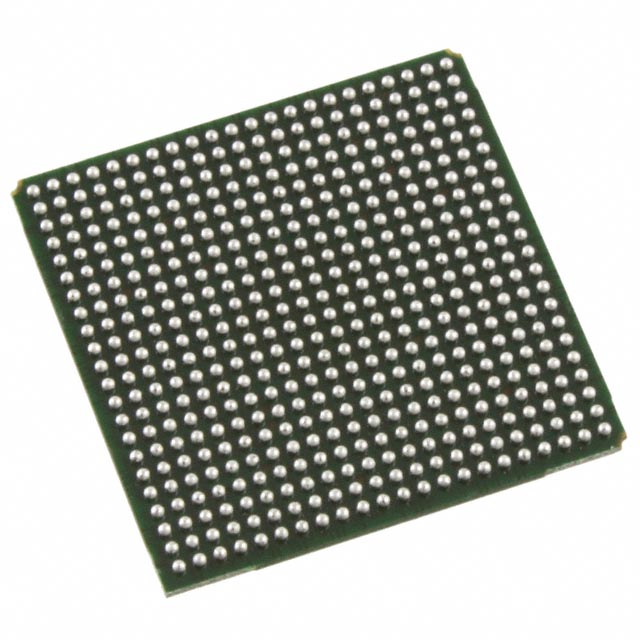

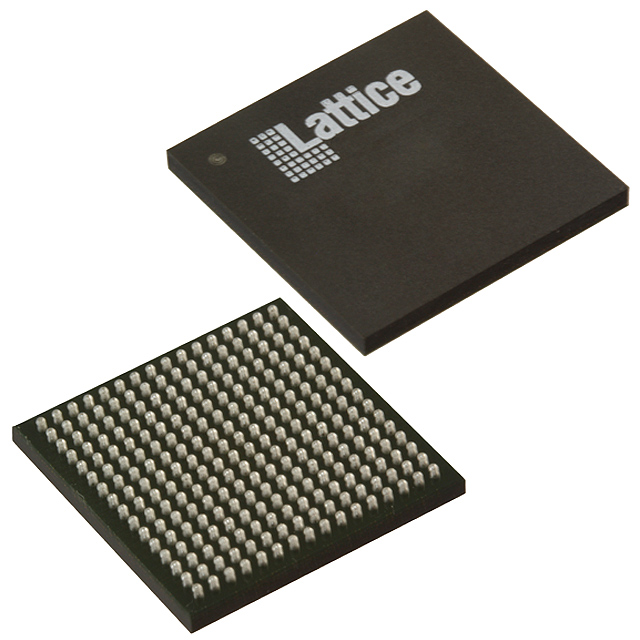

| 安裝類型 | 表面貼裝型 | |

| 系列 | ECP2M | |

| 工作温度 | 0°C ~ 85°C(TJ) | |

| 包裝 | 託盤 | |

| 封裝/外殼 | 484-BBGA | |

| 產品狀態 | 在售 | |

| 供應商器件封裝 | 484-FPBGA(23x23) | |

| 可編程 | 未驗證 | |

| LAB/CLB 數 | 2375 | |

| 邏輯元件/單元數 | 19000 | |

| 總 RAM 位數 | 1246208 | |

| I/O 數 | 304 |

部落格

¥45.00

價格更新:一個月前

Lattice Semiconductor Corporation

Lattice Semiconductor 是低功耗可編程的領導者。 在不斷增長的通信、計算、工業、汽車和消費市場中,他們通過網絡解決客户問題,從邊緣到雲端。 他們的技術、長期合作關係以及對世界級支持的承諾讓他們的客户能夠快速、輕鬆地釋放他們的創新,以創造一個智能、安全和互聯的世界。

查看所有産品從 Lattice Semiconductor Corporation熱門産品

部落格

熱門製造商

View all manufactures 更多熱門產品

更多電子零件 更多

LFE2M20SE-7FN484C

IC FPGA 304 I/O 484FBGA

ICE40LP384-SG32

IC FPGA 21 I/O 32QFN

LCMXO2-256HC-5SG32C

IC FPGA 21 I/O 32QFNS

ICE40HX1K-VQ100

IC FPGA 72 I/O 100TQFP

ICE40LP1K-CB121

IC FPGA 92 I/O 121CSBGA

ICE40HX4K-BG121

IC FPGA 93 I/O 121CABGA

LCMXO2-1200HC-6TG100C

IC FPGA 79 I/O 100TQFP

LIF-MD6000-6JMG80I

IC FPGA 37 I/O 80CTFBGA

LIA-MD6000-6JMG80E

IC FPGA 37 I/O 80CTFBGA

LCMXO3LF-6900E-6MG256C

IC FPGA 206 I/O 256CSFBGA