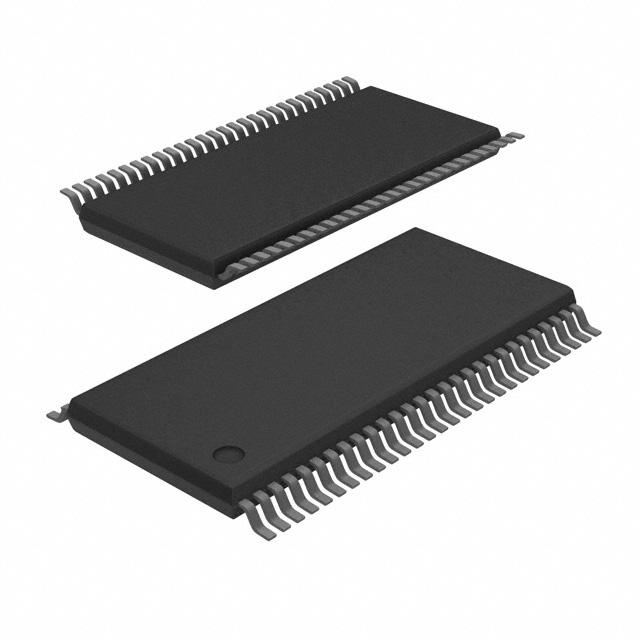

SN74ALVCH162601DLR

NOTE: For tape-and-reel order entry, the DGGR package is abbreviated to GR.Widebus, EPIC, UBT are trademarks of Texas Instruments.

Texas InstrumentsSN74ALVCH162601DLRThis 18-bit universal bus transceiver is designed for 1.65-V to 3.6-V VCC operation.

The SN74ALVCH162601DLR combines D-type latches and D-type flip-flops to allow data flow in transparent, latched, clocked, and clock-enabled modes.

Data flow in each direction is controlled by output-enable (OEAB\ and OEBA\), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB\ and CLKENBA\) inputs. For A-to-B data flow, the device operates in the transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. When OEAB\ is low, the outputs are active. When OEAB\ is high, the outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B, but uses OEBA\, LEBA, CLKBA, and CLKENBA\.

The B-port outputs include equivalent 26- series resistors to reduce overshoot and undershoot.

To ensure the high-impedance state during power up or power down, OE\ should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVCH162601DLR is characterized for operation from –0°C to 85°C.

Feature

- Member of the Texas Instruments Widebus Family

- EPIC (Enhanced-Performance Implanted CMOS) Submicron Process

- UBT (Universal Bus Transceiver) Combines D-Type Latches and D-Type Flip-Flops for Operation in Transparent, Latched, Clocked, or Clock-Enabled Modes

- B-Port Outputs Have Equivalent 26- Series Resistors, So No External Resistors Are Required

- ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

- Latch-Up Performance Exceeds 250 mA Per JESD 17

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Package Options Include Plastic 300-mil Shrink Small-Outline (DL) and Thin Shrink Small-Outline (DGG) Packages

產品屬性

| 類型 | 描述 | 全選 |

|---|---|---|

| 系列 | 74ALVCH | |

| 包裝 | 卷帶(TR) | |

| 產品狀態 | 在售 | |

| 邏輯類型 | 通用總線收發器 | |

| 電路數 | 18 位 | |

| 電流 - 輸出高、低 | 24mA,24mA;12mA,12mA | |

| 電壓 - 供電 | 1.65V ~ 3.6V | |

| 工作温度 | -40°C ~ 85°C | |

| 安裝類型 | 表面貼裝型 | |

| 封裝/外殼 | 56-BSSOP(0.295",7.50mm 寬) | |

| 供應商器件封裝 | 56-SSOP |

¥17.42

價格更新:一個月前

Texas Instruments

德州儀器 (TI) 是一家開發模擬 IC 和嵌入式處理器的全球半導體設計和製造公司。 通過聘用世界上最聰明的人才,TI 創造了塑造技術未來的創新。 今天,TI 正在幫助超過 100,000 家客户改變未來。

查看所有産品從 Texas Instruments熱門産品

部落格

熱門製造商

View all manufactures 更多熱門產品

更多電子零件 更多

SN74ALVCH162601DLR

IC UNIV BUS TXRX 18BIT 56SSOP

SN74VMEH22501DGVR

IC UNIVERSAL BUS TXRX 48TVSOP

CY74FCT16500CTPVCT

IC UNIV BUS TXRX 18BIT 56SSOP

SN74ABTH18504APM

IC SCAN TEST UNIV TXRX 64LQFP

SN74ABTH182502APM

IC SCAN TEST UNIV TXRX 64LQFP

CY74FCT16501ATPVC

IC UNIV BUS TXRX 18BIT 56SSOP

SN74VMEH22501ADGVR

IC UNIVERSAL BUS TXRX 48TVSOP

CD74HC299M

IC UNIV SHIFT REGISTER 20SOIC

SN74VMEH22501ADGGR

IC UNIVERSAL BUS TXRX 48TSSOP

SN74ALVCH16835DGG

BUS DRIVER, ALVC/VCX/A SERIES