- 全部分类

- 集成电路(IC)

- 开发板,套件,编程器

- 分立半导体产品

- 板安装电源

- 射频和无线

- 传感器,变送器

- 存储卡,模块

- 音频产品

- 电路保护

- 晶体,振荡器,谐振器

- 滤波器

- 隔离器

- 套件

- 创客/DIY,教育

- 光电器件

- 电源 - 外部/内部(板外)

- 继电器

- 电阻器

- 测试与计量

- 未分类

- 连接器,互连器件

- 电感器,线圈,扼流圈

- 电机,电磁阀,驱动器板/模块

- 交换机

- 电缆组件

- 嵌入式计算机

- 电容器

- 风扇,热管理

- 变压器

- 电池产品

- 产品

- 制造商

- 服务范围

- 服务行业

- 质量保证承诺

- 资源

XC9536XV-5PC44C datasheet

XC9536XV-5PC44C pdf

XC9536XV-5PC44C distributor

XC9536XV-5PC44C manufacturer

XC9536XV-5PC44C supplier

XC9536XV-5PC44C price

XC9536XV-5PC44C specification

XC9536XV-5PC44C wholesale

XC9536XV-5PC44C package

XC9536XV-5PC44C AMD

XC9536XV-5PC44C

面议

价格更新:一个月前

AMD

AMD是全可编程FPGA、SoC、MPSoC和3D IC的领先提供商。AMD独特地实现了软件定义和硬件优化的应用-推动了云计算,5G无线,嵌入式视觉和工业物联网领域的行业进步。

查看所有产品从 AMD热门产品

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情 XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情

XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情- XCZU49DR-1FSVF1760IIC ZUP RFSOC A53 FPGA 1760BGA¥240830.69 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情 BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情 XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情

XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情- XCZU49DR-1FSVF1760IIC ZUP RFSOC A53 FPGA 1760BGA¥240830.69 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情 BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

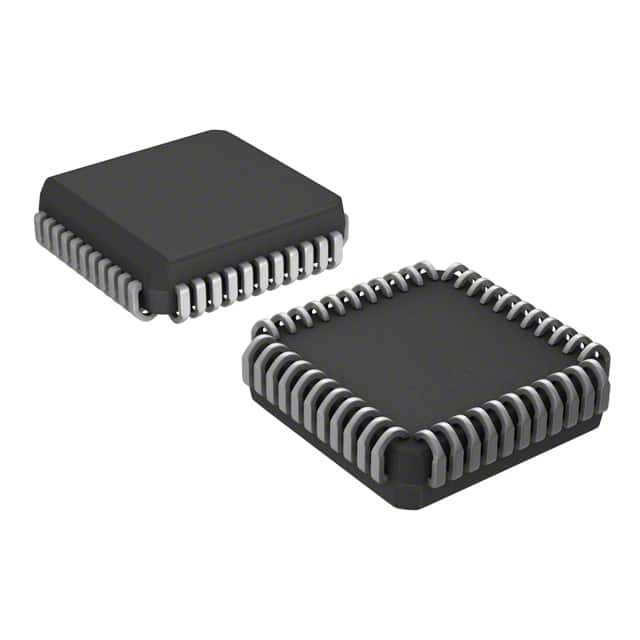

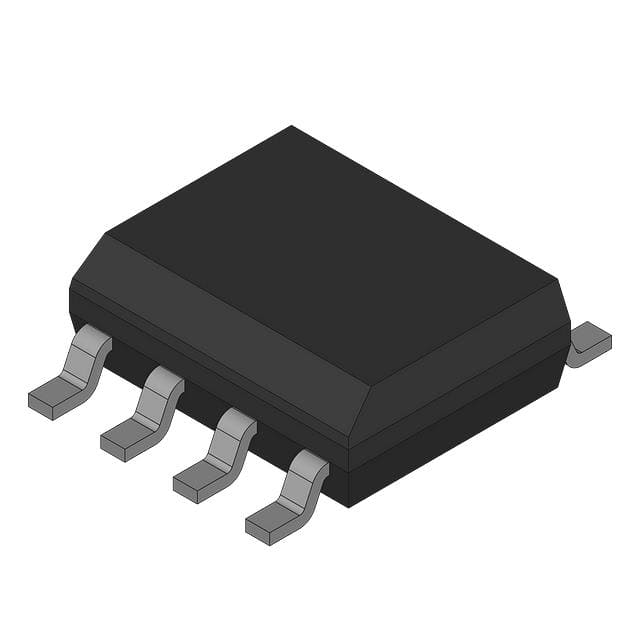

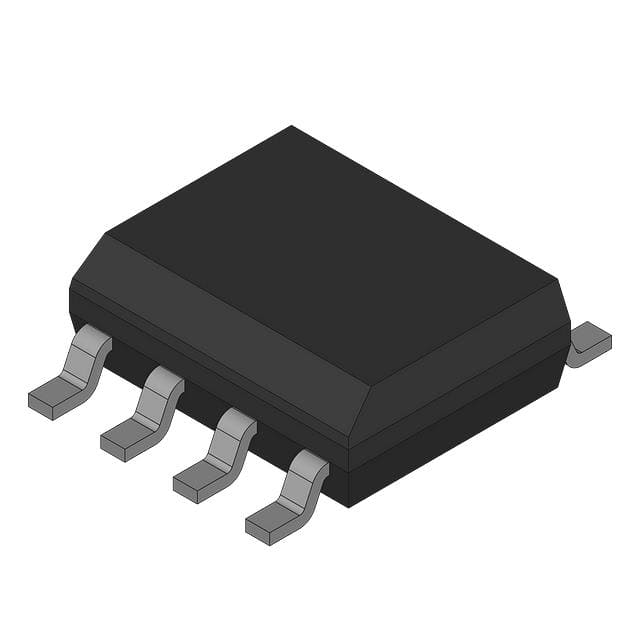

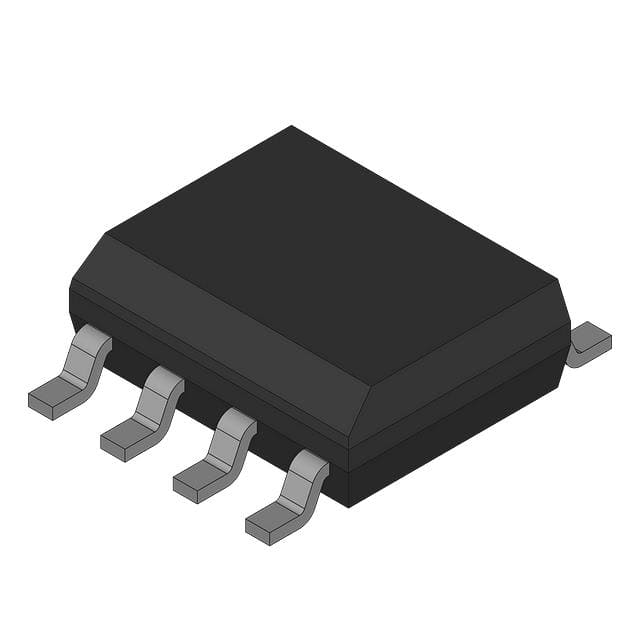

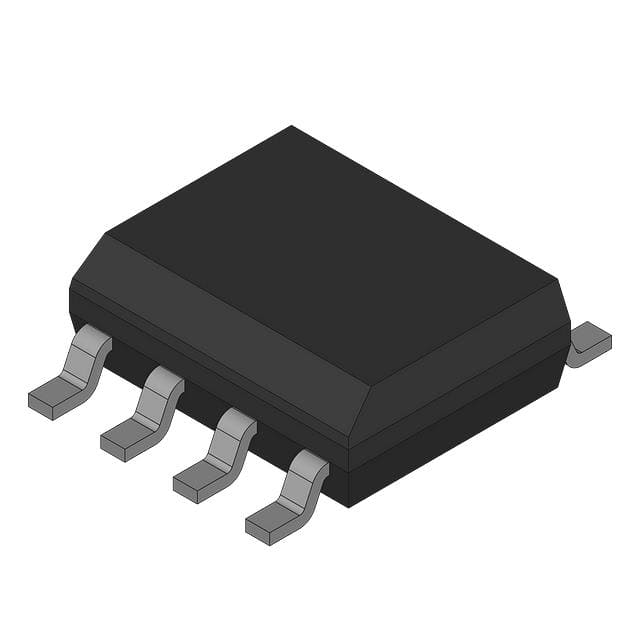

The XC9536XV-5PC44C is a 2.5V CPLD targeted for high-performance, low-voltage applications in leading-edge communications and computing systems. It is comprised of two 54V18 Function Blocks, providing 800 usable gates with propagation delays of 5 ns. See Figure 2 for architecture overview.

Power dissipation in CPLDs can vary substantially depending on the system frequency, design application and output loading. To help reduce power dissipation, each macrocell in a XC9500XV device may be configured for low-power mode (from the default high-performance mode). In addition, unused product-terms and macrocells are automatically deactivated by the software to further conserve power. For a general estimate of ICC, the following equation may be used:

PTOTAL = PINT + PIO = ICCINT x VCCINT + PIO

Separating internal and I/O power here is convenient because XC9500XV CPLDs also separate the corresponding power pins. PIO is a strong function of the load capacitance driven, so it is handled by I = CVf. ICCINT is another situation that reflects the actual design considered and the internal switching speeds. An estimation expression for ICCINT (taken from simulation) is:

ICCINT(mA) = MCHS(0.122 X PTHS + 0.238) + MCLP(0.042 x PTLP + 0.171) + 0.04(MCHS + MCLP) x fMAX x MCTOG

where:

MCHS = # macrocells used in high speed mode

MCLP = #macrocells used in low power mode

PTHS = average p-terms used per high speed macrocell

PTLP = average p-terms used over low power macrocell

fMAX = max clocking frequency in the device

MCTOG = % macrocells toggling on each clock (12% is frequently a good estimate

This calculation was derived from laboratory measurements

of an XC9500XV part filled with 16-bit counters and allowing

a single output (the LSB) to be enabled. The actual ICC

value varies with the design application and should be verified during normal system operation.

Feature

- 36 macrocells with 800 usable gates

-

Available in small footprint package

- 44-pin VQFP (34 user I/O pins)

-

Optimized for high-performance 2.5V systems

- Low power operation

- Multi-voltage operation

-

Advanced system features

- In-system programmable

- Superior pin-locking and routability with Fast CONNECT™ II switch matrix

- Extra wide 54-input Function Blocks

- Up to 90 product-terms per macrocell with individual product-term allocation

- Local clock inversion with three global and one product-term clocks

- Individual output enable per output pin

- Input hysteresis on all user and boundary-scan pin inputs

- Bus-hold circuitry on all user pin inputs

- Full IEEE Standard 1149.1 boundary-scan (JTAG)

- Fast concurrent programming

- Slew rate control on individual outputs

- Enhanced data security features

-

Excellent quality and reliability

- 20 year data retention

- ESD protection exceeding 2,000V

- Pin-compatible with 3.3V-core XC9536XL device in the 44-pin VQFP package

- 1. 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 2. 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 1. 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 1. 一旦发货,预期交货时间跟选择的运输方式有所变动。

SZC的物流和库存管理程序为您带来无与伦比的成功。

我们位于福田、龙岗、南山的战略中心为特定客户的需求提供各种定制方案。

我们还与主要物流承运商建立了长期合作关系,并提供灵活的解决方案,以满足您的个性化需求。

1. 您从我们这里购买的每个电子组件都带有365天保修期。我们对我们产品的质量负责。

2. 如果您收到的任何物品不处于完美状态,我们承诺负责任地安排退款或更换。请注意,物品必须处于原始状态,这些选项才可用。

常见问题解答:

Q: 芯能王电子有限公司如何确保XC9536XV-5PC44C是由真正制造或分销的?

A: 我们的专业商务发展部门对原始制造商和的代理进行严格的测试和资格验证。所有供应商必须通过我们的资格审查后,才允许在我们的平台上列出他们的XC9536XV-5PC44C设备。我们将XC9536XV-5PC44C产品的采购渠道和质量置于一切之上,确保彻底的供应商审计,以便您可以充满信心地进行购买。

Q: 我在哪里可以找到关于XC9536XV-5PC44C芯片的详细信息,包括原始制造商详情、CPLD(复杂可编程逻辑器件)应用和图片?

A: 使用芯能王电子有限公司的智能搜索引擎,按CPLD(复杂可编程逻辑器件)类别过滤,或者浏览的品牌页面以获取全面信息。

Q: 的XC9536XV-5PC44C在平台上显示的价格和库存水平准确吗?

A: 由于的库存出现重大波动,实时更新具有挑战性。然而,我们确保在24小时内进行定期更新。我们建议在进行付款之前,与芯能王电子有限公司的销售代表或通过我们的在线客服确认您的XC9536XV-5PC44C订单。

Q: 芯能王电子有限公司接受哪些支付方式?

A: 我们接受多种支付方式,包括TT银行、PayPal、信用卡、西联汇款和托管。

Q: 如何安排发货,并且我如何跟踪我的包裹?

A: 客户可以从行业领先的货运公司中选择,如DHL、FedEx、UPS、TNT和挂号邮件。一旦您的订单准备好发货,我们的销售团队将通知您发货详情并提供跟踪号码。请注意,跟踪信息可能需要多达24小时才能显示。通常,快递交付需要3-5天,而挂号邮件需要25-60天。

Q: XC9536XV-5PC44C的退货或更换过程是怎样的?

A: 我们对您订单中随机选取的批次进行发货前检查(PSI),以确保发货前的质量。如果XC9536XV-5PC44C未能达到您的期望,在以下条件下,我们将接受退货或更换:

- 我们承认诸如数量不正确、交付错误物品或明显的外部缺陷等问题。

- 我们在交货日期后的90天内被告知缺陷。

- XC9536XV-5PC44C保持未使用状态并且在其原始包装中。 要启动退货,请:

- 在90天期限内通知我们。

- 获取退>货授权请求。

- 更多详情,请参阅我们的退货及更换政策。

Q: 我如何获得支持或请求XC9536XV-5PC44C的数据表和引脚图?

A: 对于任何售后服务,包括XC9536XV-5PC44C的数据表和引脚图,随时通过[email protected]与我们联系

Q: 我如何联系芯能王电子有限公司?请提供具体的联系方式。

A: 通过点击我们网站右下角的客户服务按钮,直接提交RFQ,或使用我们页面顶部的“联系我们”链接通过电子邮件或电话与我们联系。我们保证在24小时内回复您的询问。

相关产品

| 制造商零件编号 | 价格(¥) | 现有数量 | |

|---|---|---|---|

XC9536XL-7VQG44IIC CPLD 36MC 7.5NS 44VQFP | 100.00 |

923

市场 | |

XC9536XL-7VQ44CIC CPLD 36MC 7.5NS 44VQFP | 34.00 |

1916

市场 | |

XC9536XL-7VQG64CIC CPLD 36MC 7.5NS 64VQFP | 78.00 |

4392

市场 | |

XC9536XL-7VQ44IIC CPLD 36MC 7.5NS 44VQFP | 40.00 |

13101

市场 | |

XC9536XL-5VQG64CIC CPLD 36MC 5NS 64VQFP | 120.00 |

900

市场 | |

XC9536XL-7CS48CIC CPLD 36MC 7.5NS 48CSBGA | 6.50 |

3980

市场 |

XC9536XL-7VQG44I

IC CPLD 36MC 7.5NS 44VQFP

100.00 对比

XC9536XL-7VQ44C

IC CPLD 36MC 7.5NS 44VQFP

34.00 对比

XC9536XL-7VQG64C

IC CPLD 36MC 7.5NS 64VQFP

78.00 对比

XC9536XL-7VQ44I

IC CPLD 36MC 7.5NS 44VQFP

40.00 对比

XC9536XL-5VQG64C

IC CPLD 36MC 5NS 64VQFP

120.00 对比

XC9536XL-7CS48C

IC CPLD 36MC 7.5NS 48CSBGA

6.50 对比

产品属性

| 类型 | 描述 | 全选 |

|---|---|---|

| 封装/外壳 | 44-LCC(J 形引线) | |

| 可编程 | 未验证 | |

| 供应商器件封装 | 44-PLCC(16.59x16.59) | |

| 可编程类型 | 系统内可编程 | |

| 延迟时间 tpd(1) 最大值 | 5 ns | |

| 供电电压 - 内部 | 2.37V ~ 2.62V | |

| 逻辑元件/块数 | 2 | |

| 宏单元数 | 36 | |

| 栅极数 | 800 | |

| I/O 数 | 34 | |

| 系列 | XC9500XV | |

| 工作温度 | 0°C ~ 70°C(TA) | |

| 包装 | 管件 | |

| 安装类型 | 表面贴装型 | |

| 产品状态 | 停产 |

博客

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。 掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。

掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。 什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。

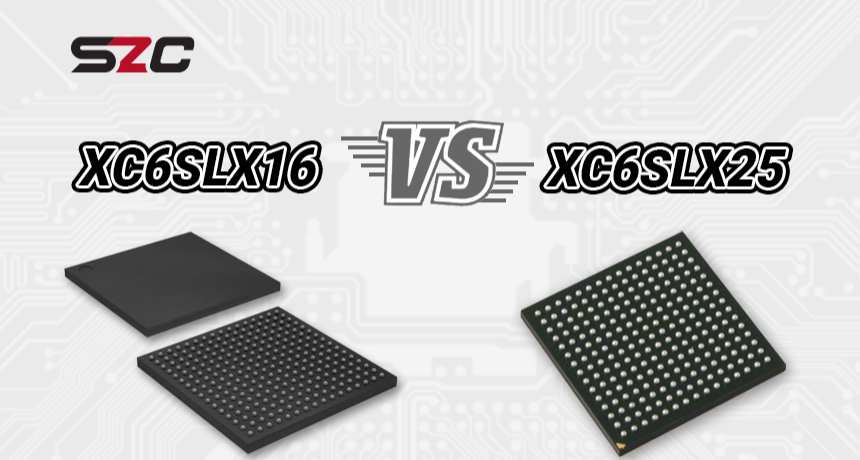

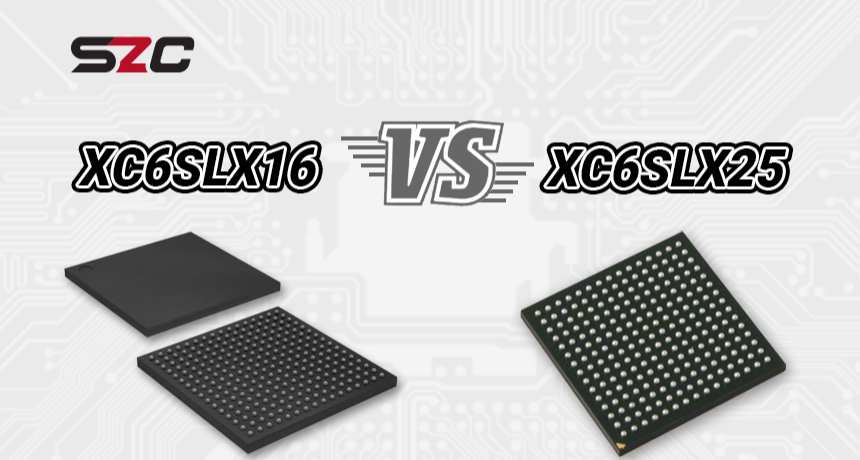

什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。 FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界!

FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界! 利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。 芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。 掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。

掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。 什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。

什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。 FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界!

FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界! 利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。 芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

面议

价格更新:一个月前

AMD

AMD是全可编程FPGA、SoC、MPSoC和3D IC的领先提供商。AMD独特地实现了软件定义和硬件优化的应用-推动了云计算,5G无线,嵌入式视觉和工业物联网领域的行业进步。

查看所有产品从 AMD热门产品

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情 XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情

XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情- XCZU49DR-1FSVF1760IIC ZUP RFSOC A53 FPGA 1760BGA¥240830.69 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情 BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情

EK-U1-VCU108-ES-G-JEVAL KIT VCU108 FPGA JAPAN面议 详情 XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情

XCZU67DR-1FSVE1156IIC ZUP RFSOC A53 FPGA 1156BGA¥132897.16 详情- XCZU49DR-1FSVF1760IIC ZUP RFSOC A53 FPGA 1760BGA¥240830.69 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情

XC2C512-10FG324CIC CPLD 512MC 9.2NS 324FBGA¥230.00 详情 BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

BNDL-OD-SE-ADVVERSALSILVER ACADEMY ENTERPRISE ADVANC¥90486.25 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情

XCVC1902-1MLIVIVA1596IC VERSAL AICORE FPGA 1596BGA¥239272.79 详情 EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情

EF-DI-LDPC-ENC-DEC-SITELOGICORE, LDPC-ENC-DEC ENCODER/D¥306765.69 详情 HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情

HW-136-CS144ADAPTER FOR 144-CSP XCR3000XL面议 详情 XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情

XC2S150E-6FT256IIC FPGA 182 I/O 256FTBGA¥15.00 详情 EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

EF-DI-CANFD-XC-SITELOGICORE, CANFD FOR NON-AUTOMOTI¥157765.21 详情

博客

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。 掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。

掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。 什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。

什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。 FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界!

FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界! 利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。 芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。

深入探讨全球陶瓷电容器市场加入我们,一起探索全球陶瓷电容器市场中的最新趋势。 掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。

掌握使用微控制器进行电流测量与与模数转换器 (ADC) 顺利配合的电压不同,电流测量增加了一层复杂性,可能导致不准确。对当前测量细微差别的探索将揭示这些误差的根源,并引入超级英雄解决方案:片上模拟核心独立外设 (CIP)。 什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。

什么是整流二极管:初学者指南揭开整流二极管的秘密!链接整流二极管的定义,应用领域,工作原理,以及常见的整流二极管。 FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界!

FPGA对比:XC6SLX16 vs. XC6SLX25通过我们的快速指南解锁fpga的秘密!XC6SLX16或xc6slx25 -哪一款是您下一次科技冒险的关键?点击现在探索可编程可能性的世界! 利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

利用onsemi的先进图像传感器增强道路安全来看看onsemi的AR0220AT吧,它是高级驾驶辅助系统(Advanced Driver Assistance Systems)中的一款夜间智能游戏颠覆者。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。

TI选择犹他州李海作为尖端半导体中心德州仪器 (TI) 选择犹他州李海作为其即将建设的 300 毫米半导体晶圆制造厂 (fab) 的选址。 芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐!

芯能王电子有限公司祝您感恩节快乐感谢您成为芯能王电子大家庭不可或缺的一员,祝您感恩节快乐! 探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。

探索 Nvidia H200 在 AI 模型训练方面的强大功能使用Nvidia的H200芯片探索AI训练的尖端可能性。解锁您的AI模型的最终潜力,并彻底改变您的工作。 XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。

XC6SLX4 vs XC6SLX9:哪个更好?利用 XC6SLX4 和 XC6SLX9 FPGA 的潜力来增强性能和多功能性。 美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

美国十大微控制器制造商本文章主要介绍美国前十微控制器制造商。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。

薄膜与陶瓷:选择适合您的电容器当我们揭开薄膜和陶瓷电容器的神秘面纱时,探索电子元件的世界。在这个技术爱好者的指南中,系好安全带,通过电容电流进行迷人的旅程。 美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗?

美国十大射频混频器制造商您准备好深入了解令人兴奋的射频混频器世界并探索美国十大制造商了吗? 热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。

热烈祝贺芯能王电子荣获“国际潜力之星分销商”奖项!芯能王电子有限公司的荣誉之旅在国际化舞台上,公司并凭借出色的表现在2023国际集成电路展览会暨研讨会上获得了享有盛誉的“国际潜力之星分销商”奖。 NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。

NCS32100:终极电感式传感器接口使用NCS32100提升您的传感解决方案,NCS32100是一种电感式传感器,可为各种静态到高速操作提供高精度的角度读数。 美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

美国十大陶瓷过滤器制造商陶瓷过滤器在各个行业中发挥着至关重要的作用,本文将为大家介绍美国十大陶瓷过滤器供应商。

热门制造商

View all manufactures 更多热门产品

更多电子零件 更多

XCR3384XL-12TQG144I

IC CPLD 384MC 10.8NS 144TQFP

XCR3064XL-10CS48C

IC CPLD 64MC 9.1NS 48CSP

XC2C64A-7VQG100I

IC CPLD 64MC 6.7NS 100VQFP

XC2C128-7VQG100C

IC CPLD 128MC 7NS 100VQFP

XC2C256-7VQG100C

IC CPLD 256MC 6.7NS 100VQFP

XCR3256XL-10TQ144I

IC CPLD 256MC 9.1NS 144TQFP

XC2C64A-7VQG100C

IC CPLD 64MC 6.7NS 100VQFP

XCR3064XL-10VQG44I

IC CPLD 64MC 9.1NS 44VQFP

XCR3064XL-6VQG100C

IC CPLD 64MC 5.5NS 100VQFP

XC2C128-7CPG132I

IC CPLD 128MC 7NS 132CSPBGA