¥5000.00

价格更新:一个月前

AMD

AMD是全可编程FPGA、SoC、MPSoC和3D IC的领先提供商。AMD独特地实现了软件定义和硬件优化的应用-推动了云计算,5G无线,嵌入式视觉和工业物联网领域的行业进步。

查看所有产品从 AMD热门产品

The CoolRunner XPLA3 (eXtended Programmable Logic Array) family of CPLDs is targeted for low power systems that include portable, handheld, and power sensitive applications. Each member of the CoolRunner XPLA3 family includes Fast Zero Power (FZP) design technology that combines low power and high speed. With this design technique, the CoolRunner XPLA3 family offers true pin-to-pin speeds of 5.0 ns, while simultaneously delivering power that is less than 56 μW at standby without the need for "turbo bits" or other power down schemes. By replacing conventional sense amplifier methods for implementing product terms (a technique that has been used in PLDs since the bipolar era) with a cascaded chain of pure CMOS gates, the dynamic power is also substantially lower than any other CPLD. CoolRunner devices are the only TotalCMOS PLDs, as they use both a CMOS process technology and the patented full CMOS FZP design technique. The FZP design technique combines fast nonvolatile memory cells with ultra-low power SRAM shadow memory to deliver the industry’s lowest power 3.3V CPLD family.

The CoolRunner XPLA3 family employs a full PLA structure for logic allocation within a function block. The PLA provides maximum flexibility and logic density, with superior pin locking capability, while maintaining deterministic timing.

CoolRunner XPLA3 CPLDs are supported by Xilinx® WebPACK™ software and industry standard CAE tools (Mentor, Cadence/OrCAD, Exemplar Logic, Synopsys, Viewlogic, and Synplicity), using HDL editors with ABEL, VHDL, and Verilog, and/or schematic capture design entry. Design verification uses industry standard simulators for functional and timing simulation. Development is supported on multiple personal computer (PC), Sun, and HP platforms.

The CoolRunner XPLA3 family features also include the industry-standard, IEEE 1149.1, JTAG interface through which boundary-scan testing, In-System Programming (ISP), and reprogramming of the device can occur. The CoolRunner XPLA3 CPLD is electrically reprogrammable using industry standard device programmers.

Feature

-

Fast Zero Power (FZP) design technique provides ultra-low power and very high speed

- Typical Standby Current of 17 to 18 μA at 25°C

- Innovative CoolRunner™ XPLA3 architecture combines high speed with extreme flexibility

- Based on industry`s first TotalCMOS PLD — both CMOS design and process technologies

-

Advanced 0.35μ five layer metal EEPROM process

- 1,000 erase/program cycles guaranteed

- 20 years data retention guaranteed

-

3V, In-System Programmable (ISP) using JTAG IEEE 1149.1 interface

- Full Boundary-Scan Test (IEEE 1149.1)

- Fast programming times

-

Support for complex asynchronous clocking

- 16 product term clocks and four local control term clocks per function block

- Four global clocks and one universal control term clock per device

- Excellent pin retention during design changes

- Available in commercial grade and extended voltage (2.7V to 3.6V) industrial grade

- 5V tolerant I/O pins

- Input register setup time of 2.5 ns

- Single pass logic expandable to 48 product terms

- High-speed pin-to-pin delays of 5.0 ns

- Slew rate control per output

- 100% routable

- Security bit prevents unauthorized access

- Supports hot-plugging capability

- Design entry/verification using Xilinx or industry standard CAE tools

-

Innovative Control Term structure provides:

- Asynchronous macrocell clocking

- Asynchronous macrocell register preset/reset

- Clock enable control per macrocell

- Four output enable controls per function block

- Foldback NAND for synthesis optimization

- Universal 3-state which facilitates "bed of nails" testing

- Available in Chip-scale BGA, Fineline BGA, and QFP packages. Pb-free available for most package types. See Xilinx Packaging for more information.

产品属性

| 类型 | 描述 | 全选 |

|---|---|---|

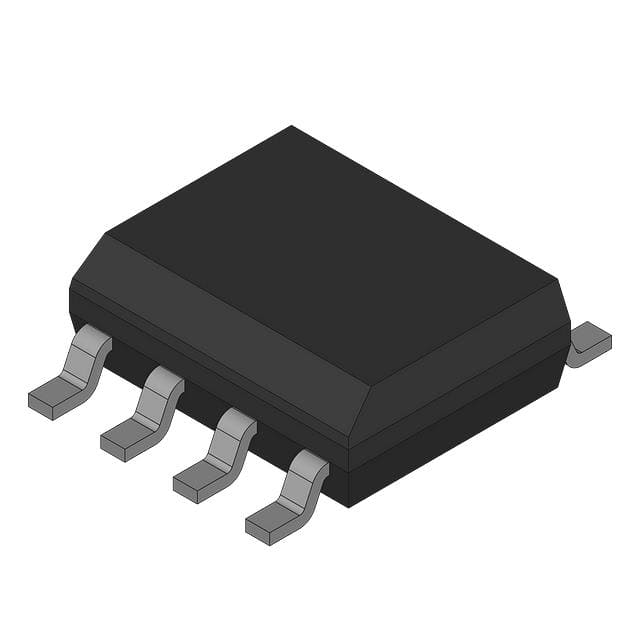

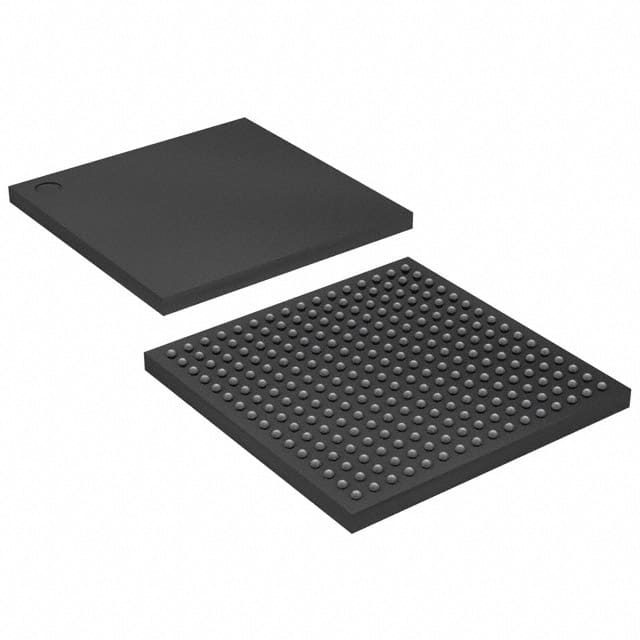

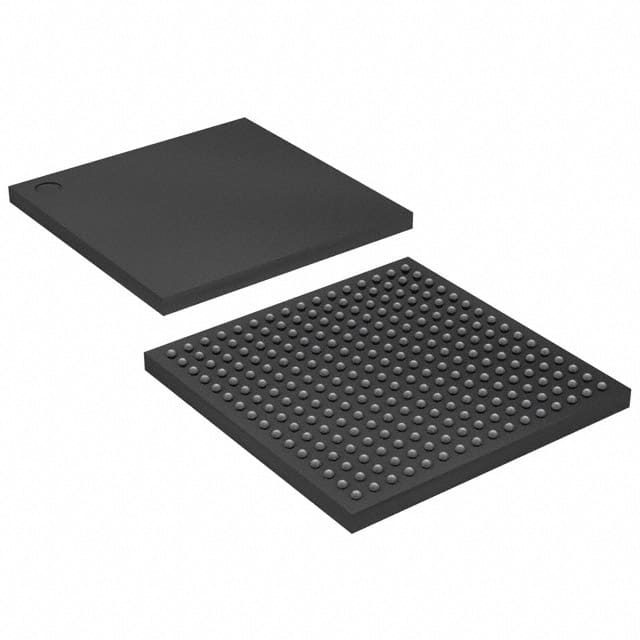

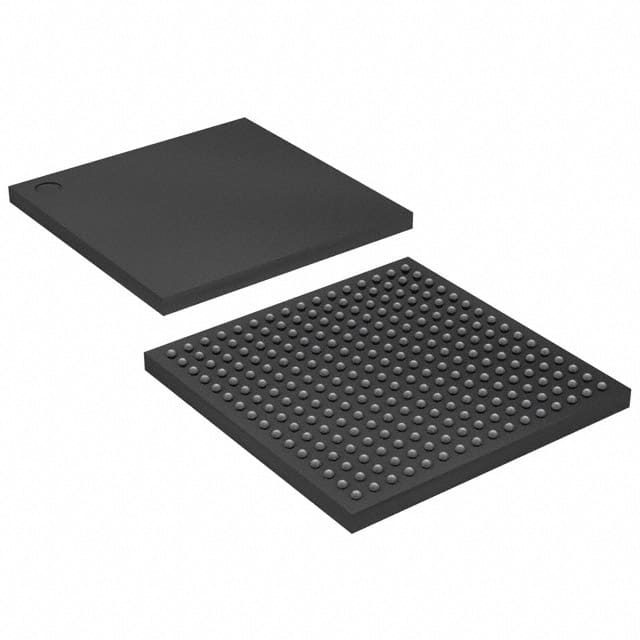

| 封装/外壳 | 256-LBGA | |

| 可编程 | 未验证 | |

| 供应商器件封装 | 256-FTBGA(17x17) | |

| 可编程类型 | 系统内可编程(最少 1K 次编程/擦除循环) | |

| 延迟时间 tpd(1) 最大值 | 9 ns | |

| 供电电压 - 内部 | 2.7V ~ 3.6V | |

| 逻辑元件/块数 | 24 | |

| 宏单元数 | 384 | |

| 栅极数 | 9000 | |

| I/O 数 | 212 | |

| 系列 | CoolRunner XPLA3 | |

| 工作温度 | -40°C ~ 85°C(TA) | |

| 包装 | 托盘 | |

| 安装类型 | 表面贴装型 | |

| 产品状态 | 在售 |

博客

¥5000.00

价格更新:一个月前

AMD

AMD是全可编程FPGA、SoC、MPSoC和3D IC的领先提供商。AMD独特地实现了软件定义和硬件优化的应用-推动了云计算,5G无线,嵌入式视觉和工业物联网领域的行业进步。

查看所有产品从 AMD热门产品

博客

热门制造商

View all manufactures 更多热门产品

更多电子零件 更多

XCR3384XL-10FT256I

IC CPLD 384MC 9NS 256FTBGA

XCR3384XL-12TQG144I

IC CPLD 384MC 10.8NS 144TQFP

XCR3064XL-10CS48C

IC CPLD 64MC 9.1NS 48CSP

XC2C64A-7VQG100I

IC CPLD 64MC 6.7NS 100VQFP

XC2C128-7VQG100C

IC CPLD 128MC 7NS 100VQFP

XC2C256-7VQG100C

IC CPLD 256MC 6.7NS 100VQFP

XCR3256XL-10TQ144I

IC CPLD 256MC 9.1NS 144TQFP

XC2C64A-7VQG100C

IC CPLD 64MC 6.7NS 100VQFP

XCR3064XL-10VQG44I

IC CPLD 64MC 9.1NS 44VQFP

XCR3064XL-6VQG100C

IC CPLD 64MC 5.5NS 100VQFP