¥5.36

价格更新:一个月前

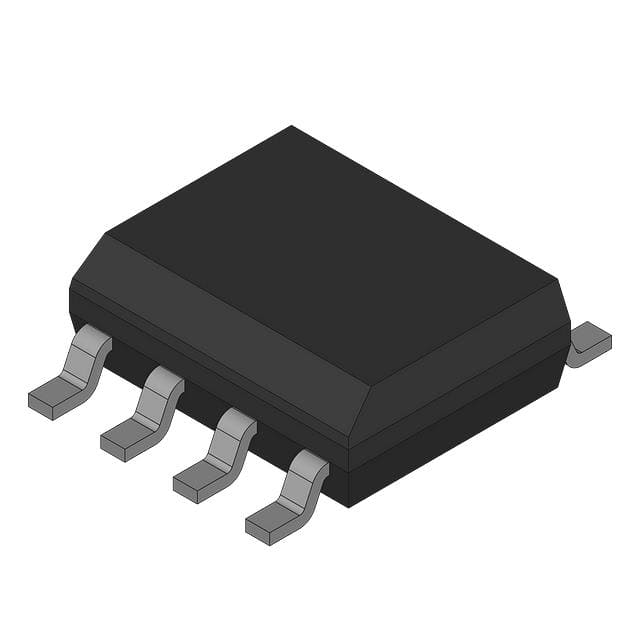

Texas Instruments

德州仪器 (TI) 是一家开发模拟 IC 和嵌入式处理器的全球半导体设计和制造公司。 通过聘用世界上最聪明的人才,TI 创造了塑造技术未来的创新。 今天,TI 正在帮助超过 100,000 家客户改变未来。

查看所有产品从 Texas Instruments热门产品

Data sheet acquired from Harris Semiconductor

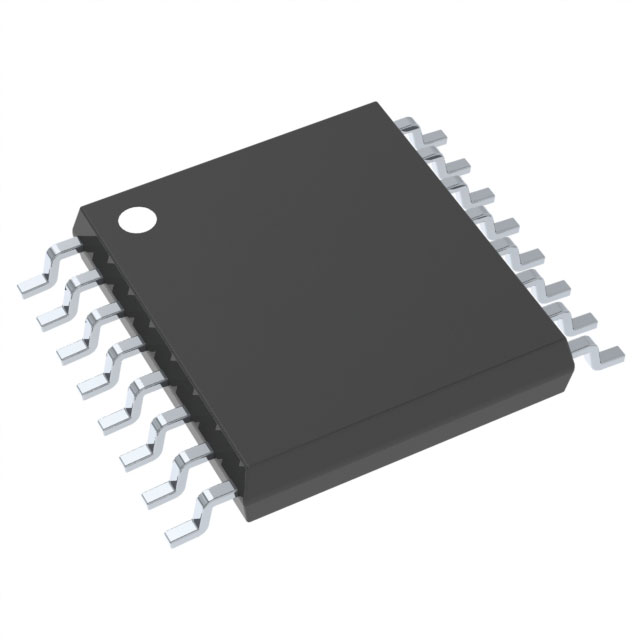

DescriptionThe device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial to parallel, or parallel to serial data transfers at very high speeds.

The two modes of operation, shift right (Q0-Q1) and parallel load, are controlled by the state of the Parallel Enable (PE)\ input. Serial data enters the first flip-flop (Q0) via the J and K\ inputs when the PE\ input is high, and is shifted one bit in the direction Q0-Q1-Q2-Q3 following each Low to High clock transition. The J and K\ inputs provide the flexibility of the JK-type input for special applications and by tying the two pins together, the simple D-type input for general applications. The device appears as four common-clocked D flip-flops when the PE\ input is Low. After the Low to High clock transition, data on the parallel inputs (D0-D3) is transferred to the respective Q0-Q3 outputs. Shift left operation (Q3-Q2) can be achieved by tying the Qn outputs to the Dn-1 inputs and holding the PE\ input low.

All parallel and serial data transfers are synchronous, occurring after each Low to High clock transition. The ’HC195 series utilizes edge triggering; therefore, there is no restriction on the activity of the J, K\, Pn and PE\ inputs for logic operations, other than set-up and hold time requirements. A Low on the asynchronous Master Reset (MR)\ input sets all Q outputs Low, independent of any other input condition.

Feature

- Asynchronous Master Reset

- J, K\,(D) Inputs to First Stage

- Fully Synchronous Serial or Parallel Data Transfer

- Shift Right and Parallel Load Capability

- Complementary Output From Last Stage

- Buffered Inputs

- Typical fMAX = 50MHz at VCC = 5V, CL = 15pF, TA = 25°C

- Fanout (Over Temperature Range)

- Standard Outputs . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . –55°C to 125°C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30%of VCC at VCC = 5V

Data sheet acquired from Harris Semiconductor

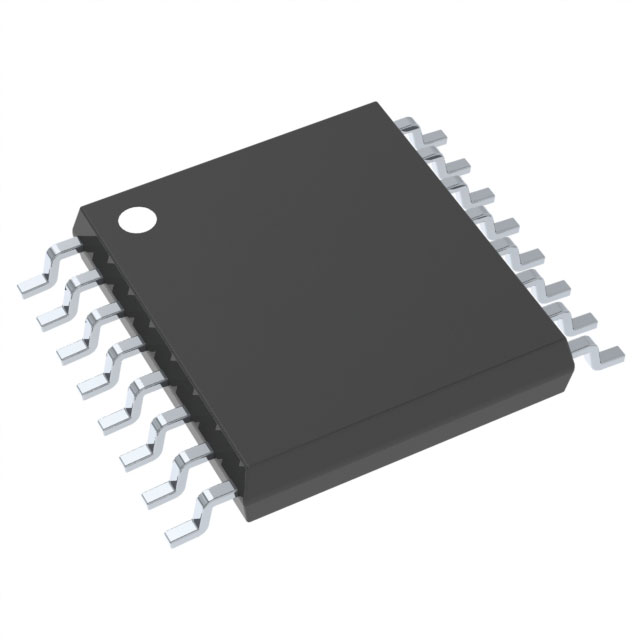

DescriptionThe device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial to parallel, or parallel to serial data transfers at very high speeds.

The two modes of operation, shift right (Q0-Q1) and parallel load, are controlled by the state of the Parallel Enable (PE)\ input. Serial data enters the first flip-flop (Q0) via the J and K\ inputs when the PE\ input is high, and is shifted one bit in the direction Q0-Q1-Q2-Q3 following each Low to High clock transition. The J and K\ inputs provide the flexibility of the JK-type input for special applications and by tying the two pins together, the simple D-type input for general applications. The device appears as four common-clocked D flip-flops when the PE\ input is Low. After the Low to High clock transition, data on the parallel inputs (D0-D3) is transferred to the respective Q0-Q3 outputs. Shift left operation (Q3-Q2) can be achieved by tying the Qn outputs to the Dn-1 inputs and holding the PE\ input low.

All parallel and serial data transfers are synchronous, occurring after each Low to High clock transition. The ’HC195 series utilizes edge triggering; therefore, there is no restriction on the activity of the J, K\, Pn and PE\ inputs for logic operations, other than set-up and hold time requirements. A Low on the asynchronous Master Reset (MR)\ input sets all Q outputs Low, independent of any other input condition.

产品属性

| 类型 | 描述 | 全选 |

|---|---|---|

| 系列 | 74HC | |

| 包装 | 卷带(TR) | |

| 产品状态 | 在售 | |

| 逻辑类型 | 双向寄存器 | |

| 输出类型 | 补充型 | |

| 元件数 | 1 | |

| 每个元件位数 | 4 | |

| 功能 | 通用 | |

| 电压 - 供电 | 2V ~ 6V | |

| 工作温度 | -55°C ~ 125°C | |

| 安装类型 | 表面贴装型 | |

| 封装/外壳 | 16-TSSOP(0.173",4.40mm 宽) | |

| 供应商器件封装 | 16-TSSOP |

博客

¥5.36

价格更新:一个月前

Texas Instruments

德州仪器 (TI) 是一家开发模拟 IC 和嵌入式处理器的全球半导体设计和制造公司。 通过聘用世界上最聪明的人才,TI 创造了塑造技术未来的创新。 今天,TI 正在帮助超过 100,000 家客户改变未来。

查看所有产品从 Texas Instruments热门产品

博客

热门制造商

View all manufactures 更多热门产品

更多电子零件 更多

CD74HC195PWR

IC 4-BIT ACCESS REGISTER 16TSSOP

CD74HC299E

CD74HC299 HIGH SPEED CMOS LOGIC

SN74LS299N

SN74LS299 UNIVERSAL SHIFT / STOR

SN74ALS164ADE4

IC SHIFT REG 8BIT PARALL 14-SOIC

SN74LS595NE4

IC 8BIT SHFT REG OUT LTCH 16-DIP

SN74HCS164QPWRQ1

AUTOMOTIVE 8-BIT SERIAL-IN/PARAL

SNJ54S195FK

PARALLEL IN PARALLEL OUT

CD74HC4094NSR

IC 8STG SHFT/STOR BUS REG 16SO

CD74HCT299M96

IC UNIV SHIFT REGISTER 20SOIC

SN74HC595DRG3

IC SHIFT REGISTER 8BIT 16SOIC