Obsolete

Analog Devices Inc./Maxim Integrated

Maxim Integrated has amalgamated with Analog Devices, imparting an augmented repertoire of superlative mixed-signal and power governance innovations, fostering clientele triumph across diverse sectors. This amalgamation begets a spectrum of resolutions for surmounting the utmost intricate quandaries, spanning from direct current to the expanse of 100 gigahertz, encompassing miniscule nanowatt realms to robust kilowatt domains, spanning the sensor continuum to the ethereal expanse of cloud. Delve deeper into Analog Devices' enriched assemblage on their product dossier.

View All Product from Analog Devices Inc./Maxim IntegratedDS2165Q/T&R FEATURES

• Compresses/expands 64kbps PCM voiceto/from either 32kbps, 24kbps, or 16kbps

• Dual fully independent channel architecture;device can be programmed to perform either:

•

•

• one expansion and one compressionInterconnects directly to combo-codecdevices

•Input to output delay is less than 375

•s

• Simple serial port used to configure thetwo expansionstwo compressions

•device

• On-board time-slot assigner-circuit (TSAC)function allows data to be input/output atvarious time slots

• Supports Channel Associated Signaling

• Each channel can be independently idled orplaced into bypass

• Available hardware mode requires no hostprocessor; ideal for voice storageapplications

• Single +5V supply; low-power CMOStechnology

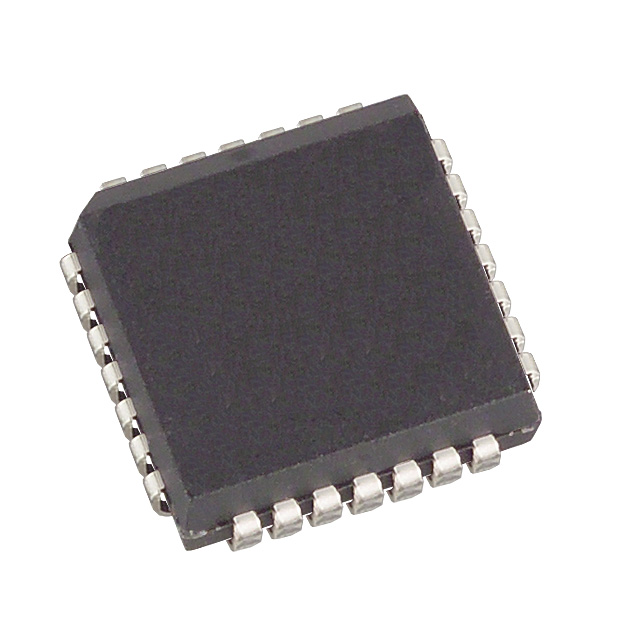

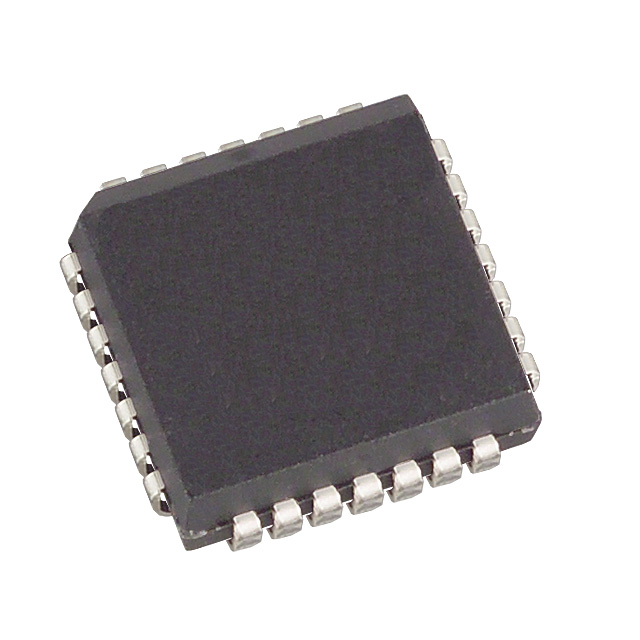

• Available in 28-pin PLCC

• 3V operation version is available(DS2165QL)

DS2165Q/T&R DESCRIPTION

The DS2165Q ADPCM processor chip is a dedicated digital-signal-processing (DSP) chip that has beenoptimized to perform adaptive-differential pulse-code modulation (ADPCM) speech compression at threedifferent rates. The chip can be programmed to compress (expand) 64kbps voice data down to (up from)either 32kbps, 24kbps, or 16kbps. The compression to 32kbps follows the algorithm specified by CCITTRecommendation G.721 (July 1986) and ANSI document T1.301 (April 1987). The compression to24kbps follows ANSI document T1.303. The compression to 16kbps follows a proprietary algorithmdeveloped by Dallas Semiconductor. The DS2165Q can switch compression algorithms on-the-fly. Thisallows the user to make maximum use of the available bandwidth on a dynamic basis.Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiplerevisions of any device may be simultaneously available through various sales channels. For information about device errata,click here: http://www.maxim-ic.com/errata.1 of 17070802

DS2165Q/T&R applications

DS2165Q/T&R Table 1. PIN DESCRIPTION

PINSYMBOLTYPE23467891011121314161718202122232425262728RSTTM0TM1A0A1A2A3A4A5SPSMCLKVSSXINCLKXFSXXOUTSCLKSDICSYOUTFSYCLKYYINVDDIIIII—IIIOIIIOIII—FUNCTIONReset. A high-low-high transition resets the algorithm. The device should bereset on power-up and when changing to or from the hardware mode.Test Modes 0 and 1. Connect to VSS for normal operation.Address Select. A0 = LSB, A5 = MSB. Must match address/command wordto enable the serial port.Serial Port Select. Connect to VDD to select the serial port; connect to VSS toselect the hardware mode.Master Clock. 10MHz clock for the ADPCM processing engine; may beasynchronous to SCLK, CLKX, and CLKY.Signal Ground. 0VX Data In. Sampled on falling edge of CLKX during selected time slots.X Data Clock. Data clock for the X-side PCM interface; must besynchronous with FSX.X Frame Sync. 8kHz frame sync for the X-side PCM interface.X Data Output. Updated on rising edge of CLKX during selected time slots.Serial Data Clock. Used to write to the serial port registers.Serial Data In. Data for on-board control registers; sampled on the risingedge of SCLK. LSB sent first.Chip Select. Must be low to write to the serial port.Y Data Output. Updated on rising edge of CLKY during selected time slots.Y Frame Sync. 8kHz frame sync for the Y-side PCM interface.Y Data Clock. Data clock for the Y-side PCM interface; must besynchronous with FSY.Y Data In. Sampled on falling edge of CLKY during selected time slots.Positive Supply. 5.0V (3.0V for DS2165QL)3 of 17

Product Attributes

| TYPE | DESCRIPTION | Select all |

|---|---|---|

| Clock Rate | 10MHz | |

| Non-Volatile Memory | - | |

| On-Chip RAM | - | |

| Voltage - I/O | 5.00V | |

| Voltage - Core | 5.00V | |

| Operating Temperature | 0°C ~ 70°C (TA) | |

| Series | - | |

| Mounting Type | Surface Mount | |

| Package | Tape & Reel (TR) | |

| Package / Case | 28-LCC (J-Lead) | |

| Product Status | Obsolete | |

| Supplier Device Package | 28-PLCC (11.51x11.51) | |

| Type | ADPCM | |

| Interface | ADPCM, PCM |

Obsolete

Analog Devices Inc./Maxim Integrated

Maxim Integrated has amalgamated with Analog Devices, imparting an augmented repertoire of superlative mixed-signal and power governance innovations, fostering clientele triumph across diverse sectors. This amalgamation begets a spectrum of resolutions for surmounting the utmost intricate quandaries, spanning from direct current to the expanse of 100 gigahertz, encompassing miniscule nanowatt realms to robust kilowatt domains, spanning the sensor continuum to the ethereal expanse of cloud. Delve deeper into Analog Devices' enriched assemblage on their product dossier.

View All Product from Analog Devices Inc./Maxim IntegratedYou May Also Be Interested In

More Electronic Parts More

DS2165Q

IC PROC ADPCM 16/24/32K 28-PLCC

DS2165N

DS2165 16/24/32 KILO BITS PER SE

DS2165

32 KB PER SECOND ADPCM PROCESSOR

DS2165Q+T&R

IC PROC ADPCM 16/24/32K 28-PLCC

DSPB56374AF

DIGITAL SIGNAL PROCESSOR, 24-BIT

MC68882EI16A

MATH COPROCESSOR, SUPPORTS MC680

DSP56004FJ66

DIGITAL SIGNAL PROCESSOR, 24-BIT

DSPC56371AF150

DSP, 24 BIT SIZE PQFP80

DSP56303VF100

DSP, 24-EXT BIT, 100MHZ, CMOS, P

DSP56311VF150

DSP, 24-EXT BIT, 150MHZ PBGA196