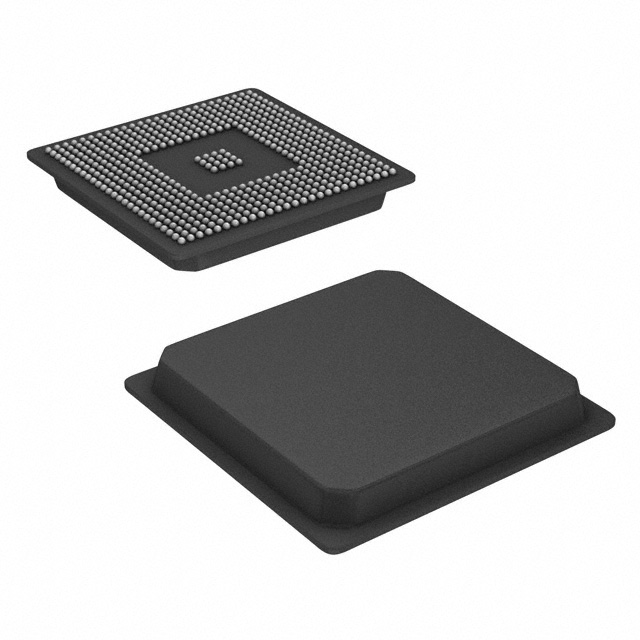

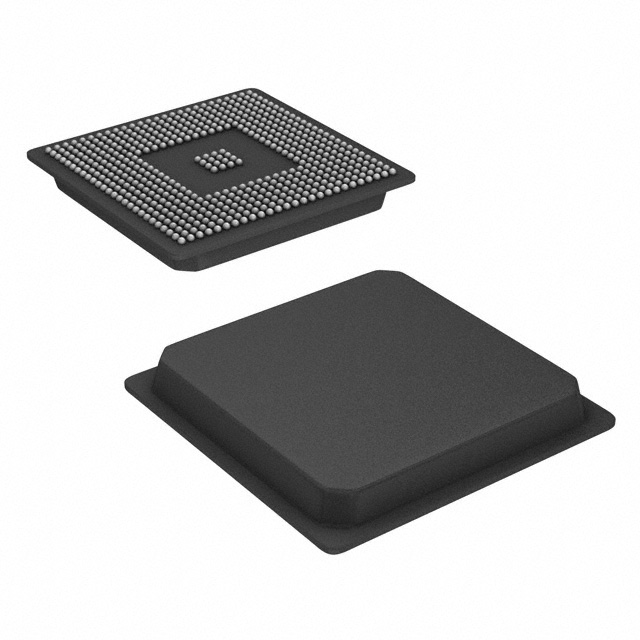

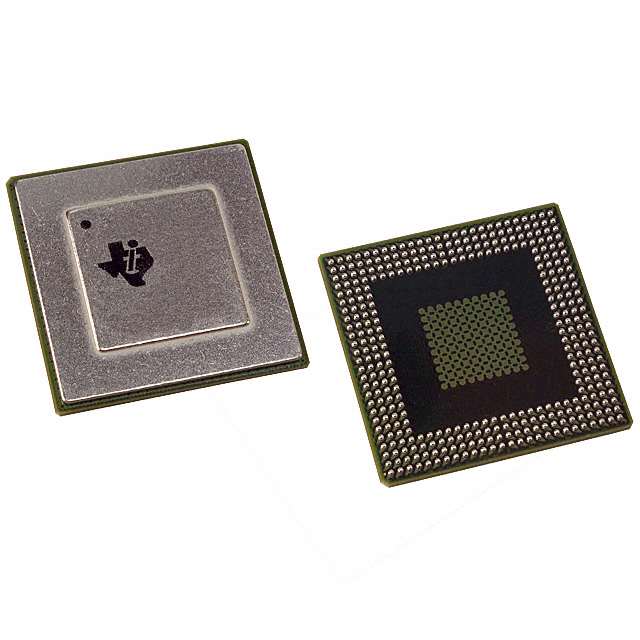

TMS320C6412AZNZ5

$20.72

Texas Instruments

Texas Instruments Incorporated (TI) is a global semiconductor powerhouse, crafts advanced analog ICs and embedded processors. Fueled by top-tier minds, TI's innovations drive tech's future, impacting 100,000+ clients.

View All Product from Texas InstrumentsTMS320C6412AZNZ5 Features

TMS320C6412AZNZ5 Description

The TMS320C64x™ DSPs (including the TMS320C6412 device) are the highest-performance fixed-pointDSP generation in the TMS320C6000™ DSP platform. The TMS320C6412 (C6412) device is based on thesecond-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture(VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for multichanneland multifunction applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.With performance of up to 5760 million instructions per second (MIPS) at a clock rate of 720 MHz, the C6412device offers cost-effective solutions to high-performance DSP programming challenges. The C6412 DSPpossesses the operational flexibility of high-speed controllers and the numerical capability of arrayprocessors. The C64x™ DSP core processor has 64 general-purpose registers of 32-bit word length and eighthighly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)—with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructionsto accelerate the performance in applications and extend the parallelism of the VelociTI™ architecture. TheC6412 can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs persecond (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. The C6412 DSP also hasapplication-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the otherC6000™ DSP platform devices.The C6412 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. TheLevel 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 2-Mbit memory space that isshared between program and data space. L2 memory can be configured as mapped memory, cache, orcombinations of the two. The peripheral set includes: a 10/100 Mb/s Ethernet MAC (EMAC); a managementdata input/output (MDIO) module; an inter-integrated circuit (I2C) Bus module; two multichannel bufferedserial ports (McBSPs); three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-portinterface (HPI16/HPI32); a peripheral component interconnect (PCI); a 16-pin general-purpose input/outputport (GP0) with programmable interrupt/event generation modes; and a 64-bit glueless external memoryinterface (EMIFA), which is capable of interfacing to synchronous and asynchronous memories andperipherals.The ethernet media access controller (EMAC) provides an efficient interface between the C6412 DSP coreprocessor and the network. The C6412 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second(Mbps) and 100 Mbps in either half- or full-duplex, with hardware flow control and quality of service (QOS)support. The C6412 EMAC makes use of a custom interface to the DSP core that allows efficient datatransmission and reception. For more details on the EMAC, see the TMS320C6000 DSP Ethernet MediaAccess Controller (EMAC) / Management Data Input/Output (MDIO) Module Reference Guide (literaturenumber SPRU628).The management data input/output (MDIO) module continuously polls all 32 MDIO addresses in order toenumerate all PHY devices in the system. Once a PHY candidate has been selected by the DSP, the MDIOmodule transparently monitors its link state by reading the PHY status register. Link change events are storedin the MDIO module and can optionally interrupt the DSP, allowing the DSP to poll the link status of the devicewithout continuously performing costly MDIO accesses. For more details on the MDIO port, see theTMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input/Output (MDIO)Module Reference Guide (literature number SPRU628).The I2C0 port on the TMS320C6412 allows the DSP to easily control peripheral devices and communicatewith a host processor. In addition, the standard multichannel buffered serial port (McBSP) may be used tocommunicate with serial peripheral interface (SPI) mode peripheral devices.The C6412 has a complete set of development tools which includes: a new C compiler, an assembly optimizerto simplify programming and scheduling, and a Windows™ debugger interface for visibility into source codeexecution.TMS320C6000, and C6000 are trademarks of Texas Instruments.Windows is a registered trademark of the Microsoft Corporation.Device Characteristics17April 2003 − Revised October 2010SPRS219J

Product Attributes

| TYPE | DESCRIPTION | Select all |

|---|---|---|

| Clock Rate | 500MHz | |

| Non-Volatile Memory | External | |

| On-Chip RAM | 288kB | |

| Voltage - I/O | 3.30V | |

| Voltage - Core | 1.40V | |

| Operating Temperature | 0°C ~ 90°C (TC) | |

| Series | TMS320C6410/12/13/18 | |

| Mounting Type | Surface Mount | |

| Package | Tube | |

| Package / Case | 548-BBGA, FCBGA | |

| Product Status | Active | |

| Supplier Device Package | 548-FCBGA (27x27) | |

| Type | Fixed Point | |

| Interface | Host Interface, McBSP, PCI |

$20.72

Texas Instruments

Texas Instruments Incorporated (TI) is a global semiconductor powerhouse, crafts advanced analog ICs and embedded processors. Fueled by top-tier minds, TI's innovations drive tech's future, impacting 100,000+ clients.

View All Product from Texas InstrumentsYou May Also Be Interested In

More Electronic Parts More

TMS320C6412AZNZ5

IC FIXED-POINT DSP 548-FCBGA

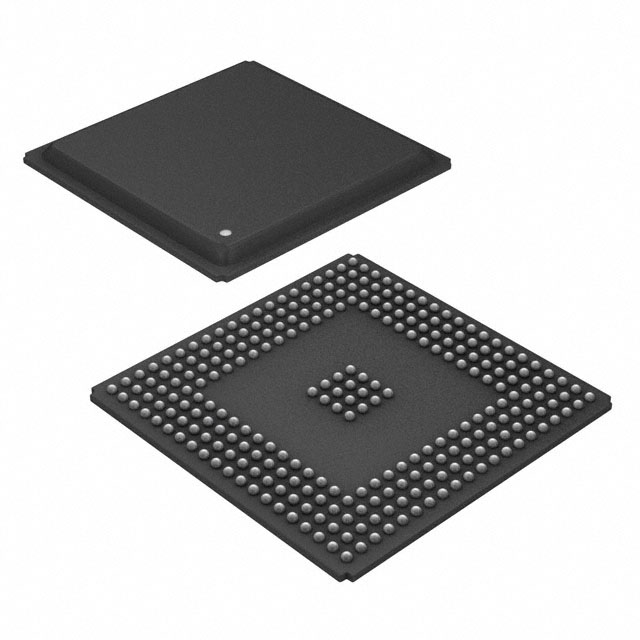

TMS320C6711DZDP200

IC DSP FLOATING-POINT 272-BGA

TMS320C203PZ80

IC DSP 100LQFP

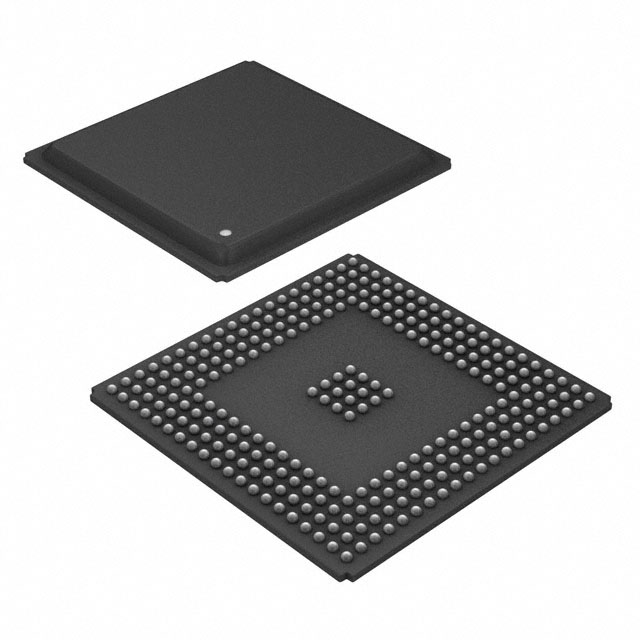

TMS320C6713BGDP225

IC FLOATING POINT DSP 272-BGA

TMS320C6701GJC150

IC FLOATING POINT DSP 352-BGA

TMS320C6416TBCLZD1

IC DSP FIXED-POINT 532FCCSP

TMS320C10FNL

DIGITAL SIGNAL PROCESSOR, 16-BIT

D172A4PZA92

100TQFP/92MHZ/95C CASE USR, DSP

TMS320C52PJ57

DIGITAL SIGNAL PROCESSOR, 16-BIT

TMS320C5505AZCHR10

CORAZON PG 2.0 100 MHZ T&R