- All categories

- Integrated Circuits (ICs)

- Development Boards, Kits, Programmers

- Discrete Semiconductor Products

- Power Supplies - Board Mount

- RF and Wireless

- Sensors, Transducers

- Memory Cards, Modules

- Audio Products

- Circuit Protection

- Crystals, Oscillators, Resonators

- Filters

- Isolators

- Kits

- Maker/DIY, Educational

- Optoelectronics

- Power Supplies - External/Internal (Off-Board)

- Relays

- Resistors

- Test and Measurement

- Uncategorized

- Connectors, Interconnects

- Inductors, Coils, Chokes

- Motors, Actuators, Solenoids and Drivers

- Switches

- Cable Assemblies

- Embedded Computers

- Capacitors

- Fans, Thermal Management

- Transformers

- Battery Products

- Products

- All categories

-

Integrated Circuits (ICs)

-

Embedded

- FPGAs (Field Programmable Gate Array)

- Microcontrollers

- CPLDs (Complex Programmable Logic Devices)

- FPGAs (Field Programmable Gate Array) with Microcontrollers

- PLDs (Programmable Logic Device)

- Microcontrollers, Microprocessor, FPGA Modules

- System On Chip (SoC)

- Application Specific Microcontrollers

- DSP (Digital Signal Processors)

- Microprocessors

-

Interface

- Drivers, Receivers, Transceivers

- Sensor and Detector Interfaces

- Analog Switches - Special Purpose

- Analog Switches, Multiplexers, Demultiplexers

- CODECS

- Controllers

- Direct Digital Synthesis (DDS)

- Encoders, Decoders, Converters

- Filters - Active

- I/O Expanders

- Modems - ICs and Modules

- Modules

- Sensor, Capacitive Touch

- Signal Buffers, Repeaters, Splitters

- Signal Terminators

- Specialized

- Telecom

- Serializers, Deserializers

- UARTs (Universal Asynchronous Receiver Transmitter)

- Voice Record and Playback

- Memory

-

Power Management (PMIC)

- DC DC Switching Controllers

- Display Drivers

- Full Half-Bridge Drivers

- Gate Drivers

- LED Drivers

- Motor Drivers, Controllers

- Power Distribution Switches, Load Drivers

- Power Management - Specialized

- Power Supply Controllers, Monitors

- Special Purpose Regulators

- Supervisors

- Voltage Regulators - DC DC Switching Regulators

- Voltage Regulators - Linear

- Voltage Regulators - Linear + Switching

- AC DC Converters, Offline Switches

- Battery Chargers

- Battery Management

- Current Regulation/Management

- Energy Metering

- Hot Swap Controllers

- Laser Drivers

- Lighting, Ballast Controllers

- OR Controllers, Ideal Diodes

- PFC (Power Factor Correction)

- Power Over Ethernet (PoE) Controllers

- RMS to DC Converters

- Thermal Management

- Voltage Reference

- Voltage Regulators - Linear Regulator Controllers

- V/F and F/V Converters

- Specialized ICs

- Audio Special Purpose

- Clock/Timing

- Data Acquisition

- Linear

-

Logic

- Buffers, Drivers, Receivers, Transceivers

- Comparators

- FIFOs Memory

- Flip Flops

- Gates and Inverters

- Gates and Inverters - Multi-Function, Configurable

- Multivibrators

- Shift Registers

- Signal Switches, Multiplexers, Decoders

- Translators, Level Shifters

- Latches

- Specialty Logic

- Counters, Dividers

- Parity Generators and Checkers

- Universal Bus Functions

-

Embedded

-

Development Boards, Kits, Programmers

- Accessories

- Evaluation and Demonstration Boards and Kits

- Evaluation Boards - DC/DC & AC/DC (Off-Line) SMPS

- Evaluation Boards - Expansion Boards, Daughter Cards

- Evaluation Boards - LED Drivers

- Evaluation Boards - Sensors

- Evaluation Boards - Embedded - Complex Logic (FPGA, CPLD)

- Evaluation Boards - Embedded - MCU, DSP

- Programmers, Emulators, and Debuggers

- Software, Services

- Evaluation Boards - Analog to Digital Converters (ADCs)

- Evaluation Boards - Audio Amplifiers

- Evaluation Boards - Digital to Analog Converters (DACs)

- Evaluation Boards - Linear Voltage Regulators

- Evaluation Boards - Op Amps

- Programming Adapters, Sockets

- RF Evaluation and Development Kits, Boards

- RFID Evaluation and Development Kits, Boards

-

Discrete Semiconductor Products

- Power Supplies - Board Mount

-

RF and Wireless

- RF Amplifiers

- Attenuators

- RF Accessories

- RF Demodulators

- RF Detectors

- RF Front End (LNA + PA)

- RF Misc ICs and Modules

- RF Mixers

- RF Modulators

- RF Power Controller ICs

- RF Power Dividers/Splitters

- RF Receivers

- RF Shields

- RF Switches

- RF Transceiver ICs

- RF Transceiver Modules and Modems

- RF Transmitters

- RFID, RF Access, Monitoring ICs

- RFID Transponders, Tags

- RF Multiplexers

- RF Receiver, Transmitter, and Transceiver Finished Units

- RF Antennas

- RFI and EMI - Contacts, Fingerstock and Gaskets

- RFID Reader Modules

- RF Circulators and Isolators

- RF Directional Coupler

- Balun

- Subscriber Identification Module (SIM) Cards

- RFID Accessories

- RFID Antennas

-

Sensors, Transducers

- Current Sensors

- Magnetic Sensors

- Position Sensors

- Specialized Sensors

- Temperature Sensors

- Motion Sensors

- Multifunction

-

Optical Sensors

- Ambient Light, IR, UV Sensors

- Image Sensors, Camera

- Photodiodes

- Distance Measuring

- Photointerrupters - Slot Type - Transistor Output

- Phototransistors

- Reflective - Analog Output

- Reflective - Logic Output

- Photo Detectors - Logic Output

- Photointerrupters - Slot Type - Logic Output

- Photoelectric, Industrial

- Camera Modules

- Photo Detectors - Remote Receiver

- Sensor, Transducer Accessories

- Sensor, Transducer Amplifiers

- Color Sensors

- Encoders

- Encoders - Industrial

- Touch Sensors

- Pressure Sensors, Transducers

- Flow Sensors

- Gas Sensors

- Pressure Sensors, Transducers - Industrial

- Float, Level Sensors

- Magnets

- Proximity Sensors

- Flow Sensors - Industrial

- Humidity, Moisture Sensors

- Memory Cards, Modules

- Audio Products

- Circuit Protection

- Crystals, Oscillators, Resonators

- Filters

- Isolators

- Kits

- Maker/DIY, Educational

-

Optoelectronics

- Circuit Board Indicators, Arrays, Light Bars, Bar Graphs

- Fiber Optic Transceiver Modules

- LED Character and Numeric

- COBs, Engines, Modules, Strips

- Color LED Lighting

- Display Bezels, Lenses

- Fiber Optic Receivers

- Fiber Optic Transmitters - Discrete

- Fiber Optic Transmitters - Drive Circuitry Integrated

- Laser Diodes, Modules

- LED Dot Matrix and Cluster

- LED Emitters - Infrared, UV, Visible

- LED Indication - Discrete

- Lenses

- Optoelectronics Accessories

- White LED Lighting

- Incandescent, Neon Lamps

- Fiber Optic Switches, Multiplexers, Demultiplexers

- Ballasts, Inverters

- LCD, OLED, Graphic

- LCD, OLED Character and Numeric

- Display, Monitor - LCD Driver/Controller

- Power Supplies - External/Internal (Off-Board)

- Relays

- Resistors

- Test and Measurement

- Uncategorized

- Connectors, Interconnects

- Inductors, Coils, Chokes

- Motors, Actuators, Solenoids and Drivers

- Switches

- Cable Assemblies

- Embedded Computers

- Capacitors

- Fans, Thermal Management

- Transformers

- Battery Products

- Manufacturers

- Services

- Industries

- Top-Quality Commitment

- Resources

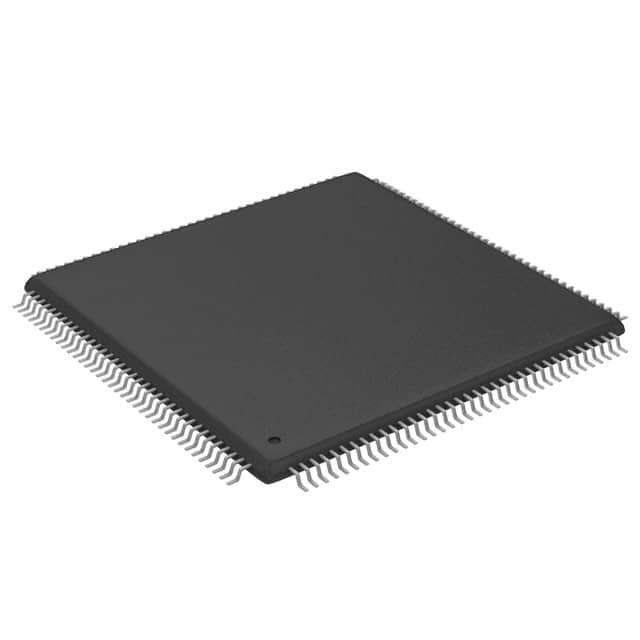

XCR3256XL-12TQG144I datasheet

XCR3256XL-12TQG144I pdf

XCR3256XL-12TQG144I distributor

XCR3256XL-12TQG144I manufacturer

XCR3256XL-12TQG144I supplier

XCR3256XL-12TQG144I price

XCR3256XL-12TQG144I specification

XCR3256XL-12TQG144I wholesale

XCR3256XL-12TQG144I package

XCR3256XL-12TQG144I Xilinx

XCR3256XL-12TQG144I

$55.12

Price update:2024-05-23

Xilinx

Xilinx stands as a preeminent purveyor of All Programmable Field-Programmable Gate Arrays (FPGAs), System on Chips (SoCs), Multiprocessor System on Chips (MPSoCs), and Three-Dimensional Integrated Circuits (3D ICs). AMD stands in a distinctive position, facilitating applications that embody a dual nature of software-defined sophistication and hardware-honed optimization. This empowering of industries finds its zenith in the realms of Cloud Computing, 5G Wireless Connectivity, Embedded Vision, and the sprawling domain of Industrial Internet of Things (IIoT).

View All Product from XilinxPopular Products

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

Introduction

The Spartan@-ll Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Features includeblock RAM(to 56K bits), distributed RAM(to 75,264 bits), 16 selectable I/O standards, and four DLLs. Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-lI family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk ofconventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary(impossible with ASICs).

Features

· Second generation ASIC replacement technology

-Densities as high as 5,292 logic cells with up to 200,000 system gates

-Streamlined features based on Virtex? FPGA architecture

-Unlimited reprogrammability

-Very low cost

-Cost-effective 0.18 micron process

· System level features

-SelectRAM TM hierarchical memory: 16bits/LUT distributed RAM Configurable 4K bit block RAM

· Fast interfaces to external RAM

-Fully PCI compliant

-Low-power segmented routing architecture

-Full readback ability for verification/observability

-Dedicated carry logic for high-speed arithmetic

-Efficient multiplier support

-Cascade chain for wide-input functions

-Abundant registers/latches with enable, set, reset

-Four dedicated DLLs for advanced clock control

-Four primary low-skew global clock distribution nets

-IEEE 1149.1 compatible boundary scan logic

·Versatile I/O and packaging

-Pb-free package options

-Low-cost packages available in all densities

-Family footprint compatibility in common packages

-16high-performance interface standards

-Hot swap Compact PCI friendly

-Zero hold time simplifies system timing

·Core logic powered at 2.5V and I/Os powered at 1.5V,2.5V,or 3.3V

·Fully supported by powerful XilinxISEdevelopment system

-Fully automatic mapping,placement,and routing

Feature

- Low power 3.3V 256 macrocell CPLD

- 7.0 ns pin-to-pin logic delays

- System frequencies up to 154 MHz

- 256 macrocells with 6,000 usable gates

- Available in small footprint packages

- 144-pin TQFP (120 user I/O pins)

- 208-pin PQFP (164 user I/O)

- 256-ball FBGA (164 user I/O)

- 280-ball CS BGA (164 user I/O)

- Optimized for 3.3V systems

- Ultra low power operation

- Typical Standby Current of 18 μA at 25° C

- 5V tolerant I/O pins with 3.3V core supply

- Advanced 0.35 micron five layer metal EEPROM process

- Fast Zero Power™ (FZP) CMOS design technology

- 3.3V PCI electrical specification compatible outputs (no internal clamp diode on any input or I/O)

- Advanced system features

- In-system programming

- Input registers

- Predictable timing model

- Up to 23 clocks available per function block

- Excellent pin retention during design changes

- Full IEEE Standard 1149.1 boundary-scan (JTAG)

- Four global clocks

- Eight product term control terms per function block

- Fast ISP programming times

- Port Enable pin for additional I/O

- 2.7V to 3.6V supply voltage at industrial grade voltage range

- Programmable slew rate control per output

- Security bit prevents unauthorized access

- Refer to the CoolRunner™ XPLA3 family data sheet (DS012) for architecture description

- 1. Shipping starts at $40, but prices may vary for certain countries like South Africa, Brazil, India, Pakistan, Israel, etc.

- 2. The basic freight for packages ≤0.5kg or equivalent volume is influenced by the time zone and country.

- 1. Our products are currently shipped using DHL, SF, and UPS. For low quantities, FedEx is the chosen carrier.

- 1. Once shipped, the estimated delivery time is contingent on the selected shipping method.

SZC's logistic and inventory management programs bring you unmatched success.

Our strategic hubs located in Futian, Longgang, Nanshan offer a variety of customized programs designed for specific customers' needs.

We also have long-standing relationships with major logistics carriers and provide flexible solutions to meet your individual requirements.

1. Every electronic component you purchase from us comes with a 365-Day Warranty. We stand behind the quality of our products.

2. Should you receive any item that isn't in perfect condition, we are committed to arranging a refund or replacement responsibly. Please note that items must be in their original condition for these options to be available.

FAQs:Q: How does SZComponents ensure that XCR3256XL-12TQG144I is genuinely manufactured or distributed by ?

A: Our professional business development department conducts rigorous testing and verification of the qualifications of original manufacturers and agents of . All suppliers must undergo and pass our qualification review before they are allowed to list their XCR3256XL-12TQG144I devices on our platform. We prioritize the sourcing channels and quality of XCR3256XL-12TQG144I products above everything else, ensuring thorough supplier audits so you can make your purchase with utmost confidence.

Q: Where can I find detailed information about XCR3256XL-12TQG144I chips, including original manufacturer details, CPLDs (Complex Programmable Logic Devices) application, and images?

A: Utilize SZComponents's intelligent search engine, filter by the CPLDs (Complex Programmable Logic Devices) category, or navigate through the 's brand page for comprehensive information.

Q: Are the prices and stock levels of 's XCR3256XL-12TQG144I shown on the platform accurate?

A: Due to significant fluctuations in 's inventory, real-time updates are challenging. However, we ensure periodic updates within 24 hours. We recommend confirming your XCR3256XL-12TQG144I order with a SZComponents sales representative or through our online customer service before proceeding with payment.

Q: What payment methods are accepted by SZComponents?

A: We accept various payment methods, including TT Bank, PayPal, Credit Card, Western Union, and Escrow.

Q: How are shipping arrangements made, and how can I track my package?

A: Customers can select from industry-leading freight companies like DHL, FedEx, UPS, TNT, and Registered Mail. Once your order is ready for shipment, our sales team will inform you about the shipping details and provide a tracking number. Note that tracking information might take up to 24 hours to appear. Typically, Express delivery takes 3-5 days, while Registered Mail requires 25-60 days.

Q: What is the process for returns or replacements of XCR3256XL-12TQG144I?

A: We conduct a Pre-Shipment Inspection (PSI) on randomly selected batches from your order to ensure quality before shipment. We will accept returns or replacements of the XCR3256XL-12TQG144I if it does not meet your expectations under the following conditions:

- Issues such as incorrect quantities, delivery of wrong items, or obvious external defects are acknowledged by us.

- We are informed about the defects within 90 days from the delivery date.

- The XCR3256XL-12TQG144I remains unused and in its original packaging.

- To initiate a return, please:

- Inform us within the 90-day period.

- Obtain a Request for Return Authorization.

- For more details, refer to our Return & Change Policy.

Q: How can I get support or request datasheets and pin diagrams for XCR3256XL-12TQG144I?

A: For any After-Sales service, including datasheets and pin diagrams for XCR3256XL-12TQG144I, feel free to contact us at [email protected]

Q: How can I contact SZComponents? Please provide specific contact methods.

A: Reach out to us by clicking the customer service button at the bottom right corner of our site, submitting an RFQ directly, or using the 'Contact Us' link at the top of our page to email or call us. We guarantee a response to your inquiries within 24 hours.

Q: How does SZComponents ensure that XCR3256XL-12TQG144I is genuinely manufactured or distributed by ?

A: Our professional business development department conducts rigorous testing and verification of the qualifications of original manufacturers and agents of . All suppliers must undergo and pass our qualification review before they are allowed to list their XCR3256XL-12TQG144I devices on our platform. We prioritize the sourcing channels and quality of XCR3256XL-12TQG144I products above everything else, ensuring thorough supplier audits so you can make your purchase with utmost confidence.

Q: Where can I find detailed information about XCR3256XL-12TQG144I chips, including original manufacturer details, CPLDs (Complex Programmable Logic Devices) application, and images?

A: Utilize SZComponents's intelligent search engine, filter by the CPLDs (Complex Programmable Logic Devices) category, or navigate through the 's brand page for comprehensive information.

Q: Are the prices and stock levels of 's XCR3256XL-12TQG144I shown on the platform accurate?

A: Due to significant fluctuations in 's inventory, real-time updates are challenging. However, we ensure periodic updates within 24 hours. We recommend confirming your XCR3256XL-12TQG144I order with a SZComponents sales representative or through our online customer service before proceeding with payment.

Q: What payment methods are accepted by SZComponents?

A: We accept various payment methods, including TT Bank, PayPal, Credit Card, Western Union, and Escrow.

Q: How are shipping arrangements made, and how can I track my package?

A: Customers can select from industry-leading freight companies like DHL, FedEx, UPS, TNT, and Registered Mail. Once your order is ready for shipment, our sales team will inform you about the shipping details and provide a tracking number. Note that tracking information might take up to 24 hours to appear. Typically, Express delivery takes 3-5 days, while Registered Mail requires 25-60 days.

Q: What is the process for returns or replacements of XCR3256XL-12TQG144I?

A: We conduct a Pre-Shipment Inspection (PSI) on randomly selected batches from your order to ensure quality before shipment. We will accept returns or replacements of the XCR3256XL-12TQG144I if it does not meet your expectations under the following conditions:

- Issues such as incorrect quantities, delivery of wrong items, or obvious external defects are acknowledged by us.

- We are informed about the defects within 90 days from the delivery date.

- The XCR3256XL-12TQG144I remains unused and in its original packaging.

- To initiate a return, please:

- Inform us within the 90-day period.

- Obtain a Request for Return Authorization.

- For more details, refer to our Return & Change Policy.

Q: How can I get support or request datasheets and pin diagrams for XCR3256XL-12TQG144I?

A: For any After-Sales service, including datasheets and pin diagrams for XCR3256XL-12TQG144I, feel free to contact us at [email protected]

Q: How can I contact SZComponents? Please provide specific contact methods.

A: Reach out to us by clicking the customer service button at the bottom right corner of our site, submitting an RFQ directly, or using the 'Contact Us' link at the top of our page to email or call us. We guarantee a response to your inquiries within 24 hours.

Related Products

| Mfr Part # | Price ($) | Quantity Available | |

|---|---|---|---|

XCR3256XL-12FTG256CIC CPLD 256MC 10.8NS 256FTBGA | 68.90 |

17

Marketplace | |

XCR3256XL-12PQ208CIC CPLD 256MC 10.8NS 208QFP | 413.40 |

298

Marketplace | |

XCR3256XL-12TQ144CIC CPLD 256MC 10.8NS 144TQFP | 55.12 |

12

Marketplace | |

XCR3256XL-10TQG144IIC CPLD 256MC 9.1NS 144TQFP | 41.34 |

3082

Marketplace | |

XCR3256XL-12FT256IIC CPLD 256MC 10.8NS 256FTBGA | 20.67 |

320

Marketplace |

XCR3256XL-12FTG256C

IC CPLD 256MC 10.8NS 256FTBGA

68.90 Compare

XCR3256XL-12PQ208C

IC CPLD 256MC 10.8NS 208QFP

413.40 Compare

XCR3256XL-12TQ144C

IC CPLD 256MC 10.8NS 144TQFP

55.12 Compare

XCR3256XL-10TQG144I

IC CPLD 256MC 9.1NS 144TQFP

41.34 Compare

XCR3256XL-12FT256I

IC CPLD 256MC 10.8NS 256FTBGA

20.67 Compare

Product Attributes

| TYPE | DESCRIPTION | Select all |

|---|---|---|

| Package / Case | 144-LQFP | |

| Programmable | Not Verified | |

| Supplier Device Package | 144-TQFP (20x20) | |

| Programmable Type | In System Programmable (min 1K program/erase cycles) | |

| Delay Time tpd(1) Max | 10.8 ns | |

| Voltage Supply - Internal | 2.7V ~ 3.6V | |

| Number of Logic Elements/Blocks | 16 | |

| Number of Macrocells | 256 | |

| Number of Gates | 6000 | |

| Number of I/O | 120 | |

| Series | CoolRunner XPLA3 | |

| Operating Temperature | -40°C ~ 85°C (TA) | |

| Package | Tray | |

| Mounting Type | Surface Mount | |

| Product Status | Active |

Blog

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation. Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging:

Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging: A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market.

A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market. Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs).

Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs). What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

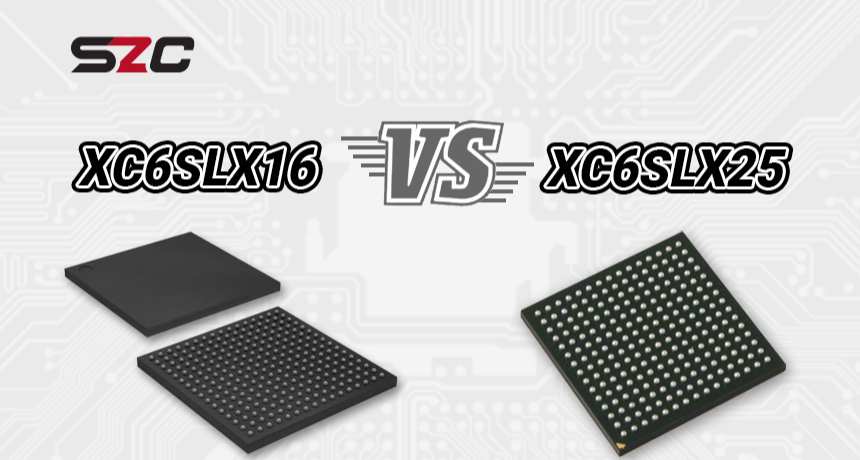

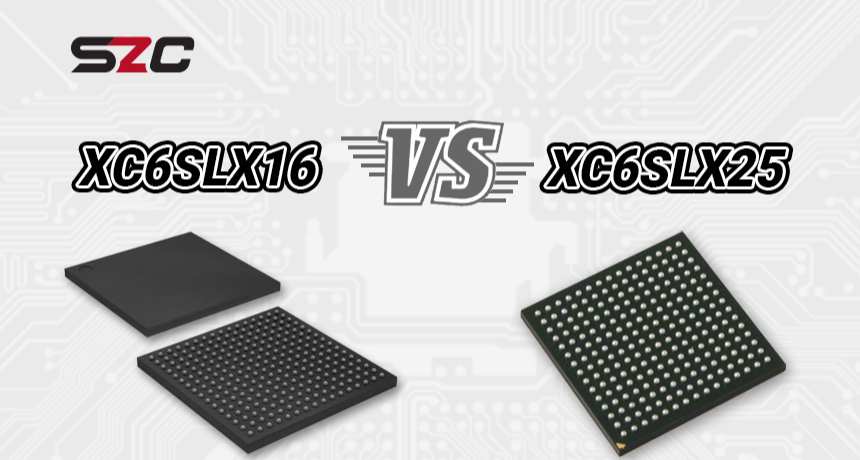

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities!

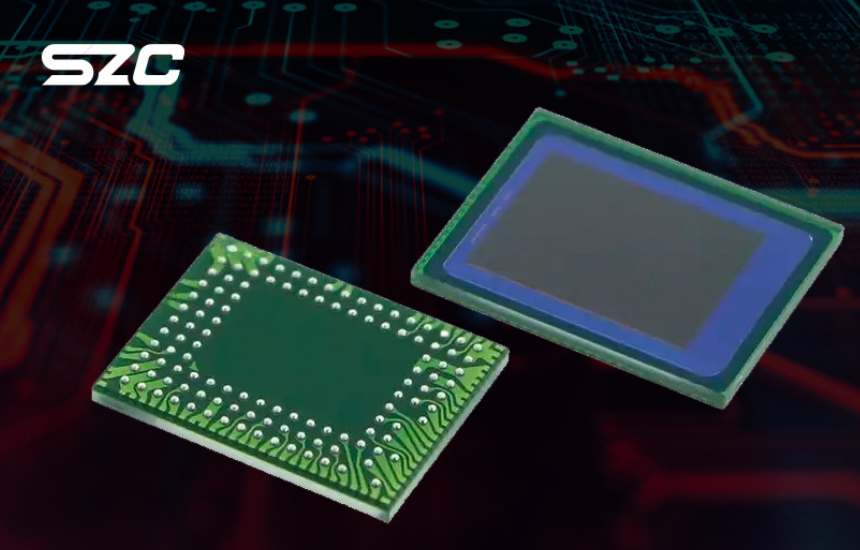

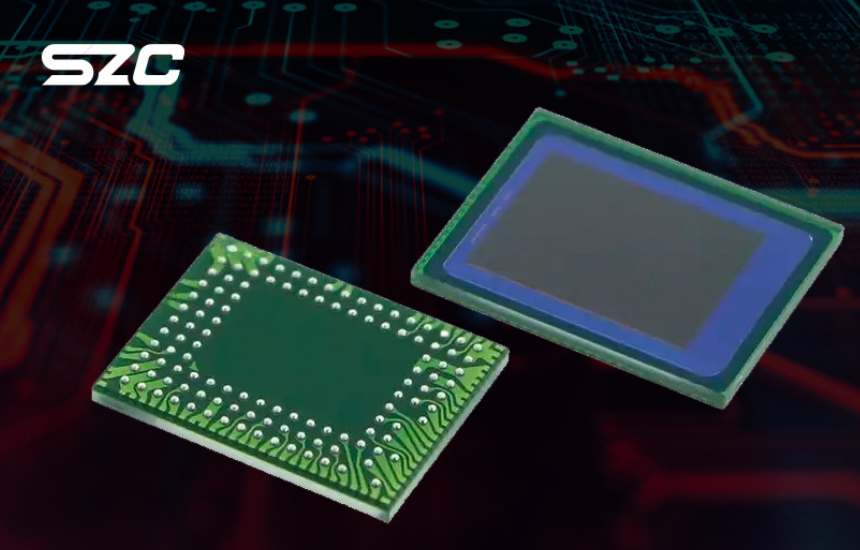

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities! Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems.

Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems. Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab).

Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab). Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving!

Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving! Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation. Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging:

Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging: A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market.

A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market. Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs).

Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs). What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities!

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities! Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems.

Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems. Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab).

Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab). Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving!

Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving! Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

$55.12

Price update:2024-05-23

Xilinx

Xilinx stands as a preeminent purveyor of All Programmable Field-Programmable Gate Arrays (FPGAs), System on Chips (SoCs), Multiprocessor System on Chips (MPSoCs), and Three-Dimensional Integrated Circuits (3D ICs). AMD stands in a distinctive position, facilitating applications that embody a dual nature of software-defined sophistication and hardware-honed optimization. This empowering of industries finds its zenith in the realms of Cloud Computing, 5G Wireless Connectivity, Embedded Vision, and the sprawling domain of Industrial Internet of Things (IIoT).

View All Product from XilinxPopular Products

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail

XC4VFX60-10FFG672IIC FPGA 352 I/O 672FCBGA$256.31 Detail- XC5VLX85-1FFG676CESIC FPGA 440 I/O 676FCBGAPrice negotiable Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail

XC7Z045-3FFG676EIC SOC CORTEX-A9 1GHZ 676FCBGA$248.04 Detail XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail

XC4085XL-3BG432IIC FPGA 352 I/O 432MBGAPrice negotiable Detail XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

XCZU9CG-2FFVB1156IIC SOC CORTEX-A53 1156FCBGA$372.06 Detail

Blog

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation. Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging:

Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging: A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market.

A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market. Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs).

Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs). What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities!

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities! Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems.

Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems. Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab).

Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab). Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving!

Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving! Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation.

Unveiling the Future: The Surge of Microcontrollers in 2024In the dynamic world of electronic components, microcontrollers stand out as a testament to innovation and versatility. As we edge closer to 2024, the landscape for microcontrollers and semiconductors, spearheaded by giants like STMicroelectronics, Texas Instruments, and Microchip, is set for remarkable transformation. Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging:

Microcontrollers vs. Microprocessors: Unveiling the Core Differences for Embedded Systems EngineeringSeasoned professionals in the realm of embedded systems engineering and product development within the electronics sphere often grapple with distinguishing between microcontrollers and microprocessors. Despite their foundational role in the design and fabrication of a myriad of electronic gadgets, understanding their unique functionalities based on mere definitions can be challenging: A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market.

A Deep Dive into the Global Ceramic Capacitors MarketJoin us in exploring the emerging subplot of environmental consciousness within the global ceramic capacitors market. Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs).

Mastering Current Measurement with MicrocontrollersUnlock precise current measurement secrets with Microcontrollers! Conquer challenges, meet superhero solutions, and revolutionize accuracy with on-chip Analog Core Independent Peripherals (CIPs). What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

What is a Rectifier Diode: A Guide to BeginnersMeet the unsung heroes of electronics—Rectifier Diodes! Explore their magic, applications, and join the behind-the-scenes adventure into gadget power.

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities!

FPGAs Face-Off: XC6SLX16 vs XC6SLX25Unlock the secrets of FPGAs with our quick guide! XC6SLX16 or XC6SLX25—Which one holds the key to your next tech adventure? Click now to explore the world of programmable possibilities! Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems.

Enhancing Road Safety with onsemi's Advanced Image SensorsMeet onsemi's AR0220AT, a night-savvy game-changer in Advanced Driver Assistance Systems. Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab).

Texas Instruments Picks Lehi, Utah for Cutting-Edge Semiconductor HubTexas Instruments (TI) has chosen Lehi, Utah, as the site for its upcoming 300-millimeter semiconductor wafer fabrication plant (fab). Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving!

Thanksgiving Greetings from SZComponentsThank you for being an integral part of the SZComponents family. Happy Thanksgiving! Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

Discover the power of Nvidia H200 for AI model trainingDiscover the cutting-edge possibilities of AI training with Nvidia's H200 chip. Unlock the ultimate potential for your AI models and revolutionize your work.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility.

XC6SLX4 vs XC6SLX9: Which One is Better?Harnessing the Potential of XC6SLX4 and XC6SLX9 FPGAs for Enhanced Performance and Versatility. Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey!

Top 10 Microcontroller Manufacturers in the USAExplore top 10 USA's microcontroller innovation, revealing top players shaping electronics. Buckle up for a game-changing journey! Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide.

Film vs. Ceramic: Choosing the Right Capacitor for YouExplore the world of electronic components as we demystify film and ceramic capacitors. Buckle up for a captivating journey through the currents of capacitance in this tech enthusiast's guide. Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation.

Explore Top 10 RF Mixer Manufacturers in the USAReady to discover the USA's top 10 RF mixer makers? Join us for an electrifying trip through innovation. SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

SZComponents Wins "International Potential Star Distributor" AwardJoin us in celebrating SZComponents' remarkable win as the "International Potential Star Distributor" and explore their journey to success.

Popular Manufacturers

View all manufactures MorePopular Parts Number

More Electronic Parts More

XCR3256XL-12TQG144I

IC CPLD 256MC 10.8NS 144TQFP

XCR3064XL-10VQG44C

IC CPLD 64MC 9.1NS 44VQFP

XC9572XL-10VQG64I

IC CPLD 72MC 10NS 64VQFP

XC2C256-7VQG100I

IC CPLD 256MC 6.7NS 100VQFP

XC9536XL-7VQG64C

IC CPLD 36MC 7.5NS 64VQFP

XC2C32A-6CP56C

IC CPLD 32MC 5.5NS 56CSBGA

XC9536XL-10VQ64I

IC CPLD 36MC 10NS 64VQFP

XCR3032XL-10VQ44C

IC CPLD 32MC 9.1NS 44VQFP

XC9536XL-7CSG48I

IC CPLD 36MC 7.5NS 48CSBGA

XCR3032XL-10CSG48I

IC CPLD 32MC 9.1NS 48CSBGA